Wireless Black Box with Mems Accelerometer

Info: 25155 words (101 pages) Dissertation

Published: 16th Dec 2019

Tagged: Engineering

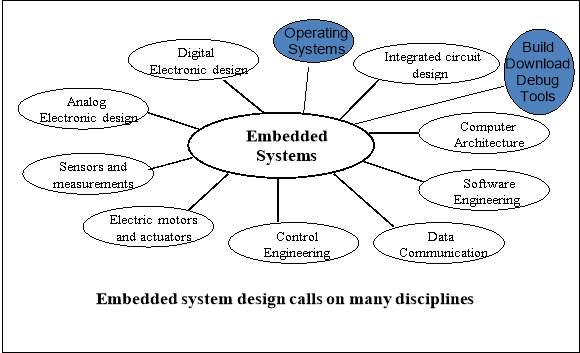

Figure 1(a): design cycles of embedded systems

EMBEDDED SYSTEM DESIGN CYCLE

Figure 1(a): design cycles of embedded systems

EMBEDDED SYSTEM DESIGN CYCLE

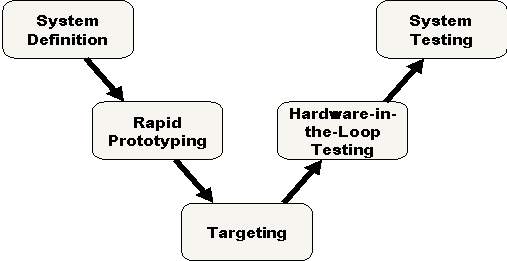

Figure.1(b):“V Diagram” of embedded systems

1.3 Characteristics of Embedded System

An embedded system is any computer system hidden inside a product other than a computer.

They will encounter a number of difficulties when writing embedded system software in addition to those we encounter when we write applications.Throughput – Our system may need to handle a lot of data in a short period of time.Response–Our system may need to react to events quickly.Testability–Setting up equipment to test embedded software can be difficult.

Debugability–Without a screen or a keyboard, finding out what the software is doing wrong (other than not working) is a troublesome problem.

Reliability – embedded systems must be able to handle any situation without human intervention

Memory space – Memory is limited on embedded systems, and you must make the software and the data fit into whatever memory exists

Program installation – you will need special tools to get your software into embedded systems

Power consumption – Portable systems must run on battery power, and the software in these systems must conserve power

Processor hogs – computing that requires large amounts of CPU time can complicate the response problem

Cost – Reducing the cost of the hardware is a concern in many embedded system projects; software often operates on hardware that is barely adequate for the job.

Embedded systems have a microprocessor/ microcontroller and a memory. Some have a serial port or a network connection. They usually do not have keyboards, screens or disk drives.

1.4 APPLICATIONS

Figure.1(b):“V Diagram” of embedded systems

1.3 Characteristics of Embedded System

An embedded system is any computer system hidden inside a product other than a computer.

They will encounter a number of difficulties when writing embedded system software in addition to those we encounter when we write applications.Throughput – Our system may need to handle a lot of data in a short period of time.Response–Our system may need to react to events quickly.Testability–Setting up equipment to test embedded software can be difficult.

Debugability–Without a screen or a keyboard, finding out what the software is doing wrong (other than not working) is a troublesome problem.

Reliability – embedded systems must be able to handle any situation without human intervention

Memory space – Memory is limited on embedded systems, and you must make the software and the data fit into whatever memory exists

Program installation – you will need special tools to get your software into embedded systems

Power consumption – Portable systems must run on battery power, and the software in these systems must conserve power

Processor hogs – computing that requires large amounts of CPU time can complicate the response problem

Cost – Reducing the cost of the hardware is a concern in many embedded system projects; software often operates on hardware that is barely adequate for the job.

Embedded systems have a microprocessor/ microcontroller and a memory. Some have a serial port or a network connection. They usually do not have keyboards, screens or disk drives.

1.4 APPLICATIONS

- Military and aerospace embedded software applications

- Communication Applications

- Industrial automation and process control software

- Mastering the complexity of applications.

- Reduction of product design time.

- Real time processing of ever increasing amounts of data.

- Intelligent, autonomous sensors.

CHAPTER 2

BLOCK DIAGRAM OF WIRELESS BLACKBOX

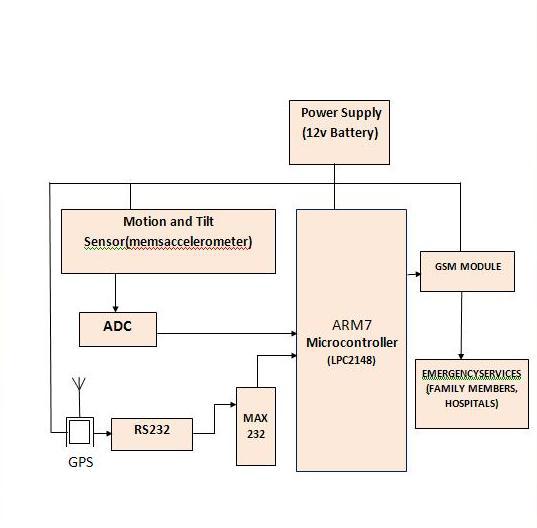

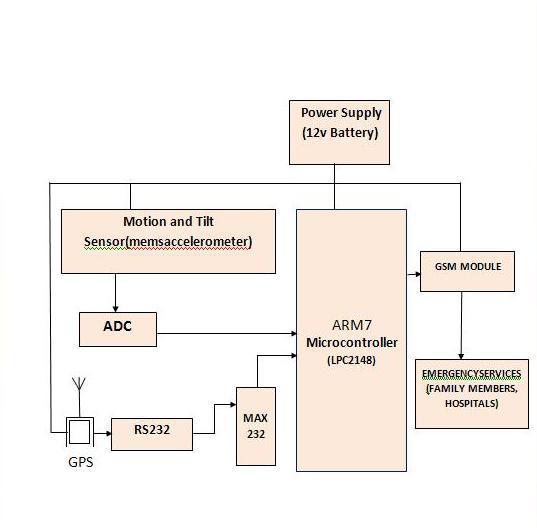

Figure.2(a):block diagram of wireless blackbox

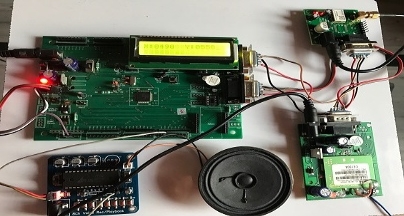

2.1 INTRODUCTION TO WIRELESS BLACK BOX

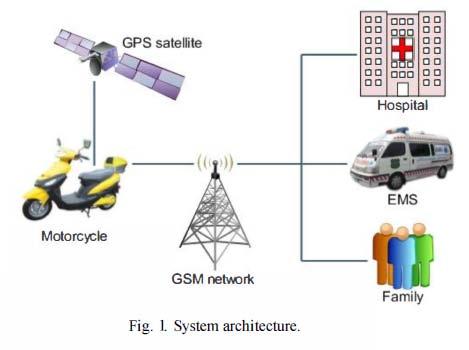

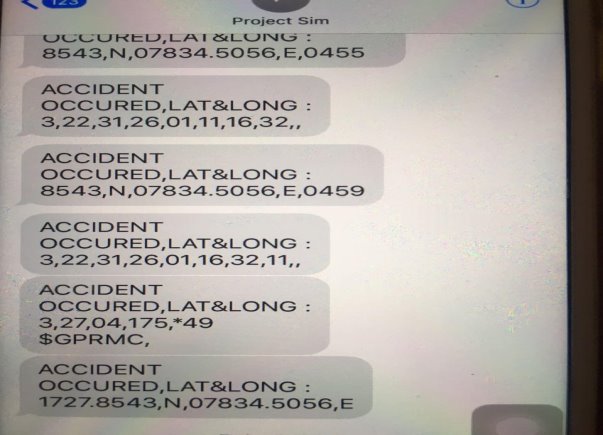

Now a day’s accidents have become a major public problem in many countries and in metropolitan cities. This problem is due to rider's poor behaviors such as speed driving, drunk driving, riding with no helmet protection, riding without sufficient sleep, etc. Many campaigns have been conducted by the people for the awareness but the numbers of death and disability are very high because of late assistance to people those who got through the accident. Therefore, several research groups and major motorcycle manufacturers including Honda have developed safety devices to protect riders from accidental injuries.Thus, fall detection and accident alarm system for two wheelers has recently gained attention because these systems are expected to save peoples life by helping riders to get medical treatment on time. In this case, wireless black box using MEMS accelerometer and GPS tracking system is developed for accidental monitoring. If any accident occurs, this wireless device will send a message from mobile phone and indicating the position of vehicle by tracking the location through GPS system to family member, emergency medical service and nearest hospital so that they can provide ambulance and prepare treatment for the patients.

This project is to develop a wireless black box using MEMS accelerometer and GPS tracking system for accidental monitoring. MEMS is a Micro electro mechanical sensor which is a high sensitive sensor and capable of detecting the tilt. This device can perform all the tilt functions like forward, reverse, left and right directions. The system consists of cooperative components of an accelerometer, microcontroller unit, GPS device and GSM module. If any accident occurs, this wireless device will send mobile phone a short massage indicating the position of vehicle by tracing the location of the vehicle through GPS system to family member, emergency medical service (EMS) and nearest hospital. . The threshold algorithm and speed of motorcycle are used to determine fall or accident in real-time. And also at the time of occurring of accident the voices of the victims are recorded using a playback recorder so that we can use it in future to know the exact cause for the occurrence of the accident so that it would be easy for the government to find evidences.

The system consists of cooperative components of an accelerometer, microcontroller unit, GPS device, Global positioning system for Mobile module, sensors for sending a short massage. An accelerometer is applied for awareness and fall detection indicating an accident. If any accident is occurred then the location of the vehicle is traced by the longitude and latitude values of GPS and sends a SMS to the nearest hospitals and family members so that they can be ready for the treatment.

2.2 Existing system

In existing system most of the people associate black boxes with airplanes but they are no longer just the key tool in investigation of airplane accidents. Presently tracking system is introduced in vehicles to avoid the accidents and save peoples life. But these systems are still installed in some of the high-end motorcycles only because these systems are too expensive for most of the motorcycle riders. In our project we are introducing fall detection and alarm system which is expected to save peoples life by detecting the accidents occurred and provides help by tracing the location of the motorcycle riders with the help of GPS technology. This provides the information of the motorcycle rider if any accident is occurred to the family members and at the same time it sends a message to the nearest hospital for the help.

2.3 Design of proposed hardware system

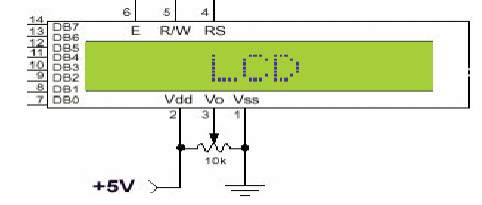

The process of working of this project is explained as follows. The total equipment of this project is placed inside a vehicle is not visible to others. Here we have MEMS accelerometer which will sense the movements of the vehicle continuously. When an accident occurs to the vehicle the movement of the vehicle while the incident is occurring will be detected by the MEMS and this information is given to microcontroller. Here we use GPS module to track the location of the vehicle where the accident has occurred. GPS can get the graphical location of the vehicle and these location values are displayed on the LCD (Liquid Crystal Display). Figure.2. Block diagram of hardware system The location values are given to microcontroller. Controller gives this information to GSM module. By using GSM we can send the message to family members, emergency medical service and nearest hospital.

CHAPTER 3

HARDWARE REQUIREMENTS

HARDWARE COMPONENTS FOR WIRELESS BACKBOX:

CHAPTER 2

BLOCK DIAGRAM OF WIRELESS BLACKBOX

Figure.2(a):block diagram of wireless blackbox

2.1 INTRODUCTION TO WIRELESS BLACK BOX

Now a day’s accidents have become a major public problem in many countries and in metropolitan cities. This problem is due to rider's poor behaviors such as speed driving, drunk driving, riding with no helmet protection, riding without sufficient sleep, etc. Many campaigns have been conducted by the people for the awareness but the numbers of death and disability are very high because of late assistance to people those who got through the accident. Therefore, several research groups and major motorcycle manufacturers including Honda have developed safety devices to protect riders from accidental injuries.Thus, fall detection and accident alarm system for two wheelers has recently gained attention because these systems are expected to save peoples life by helping riders to get medical treatment on time. In this case, wireless black box using MEMS accelerometer and GPS tracking system is developed for accidental monitoring. If any accident occurs, this wireless device will send a message from mobile phone and indicating the position of vehicle by tracking the location through GPS system to family member, emergency medical service and nearest hospital so that they can provide ambulance and prepare treatment for the patients.

This project is to develop a wireless black box using MEMS accelerometer and GPS tracking system for accidental monitoring. MEMS is a Micro electro mechanical sensor which is a high sensitive sensor and capable of detecting the tilt. This device can perform all the tilt functions like forward, reverse, left and right directions. The system consists of cooperative components of an accelerometer, microcontroller unit, GPS device and GSM module. If any accident occurs, this wireless device will send mobile phone a short massage indicating the position of vehicle by tracing the location of the vehicle through GPS system to family member, emergency medical service (EMS) and nearest hospital. . The threshold algorithm and speed of motorcycle are used to determine fall or accident in real-time. And also at the time of occurring of accident the voices of the victims are recorded using a playback recorder so that we can use it in future to know the exact cause for the occurrence of the accident so that it would be easy for the government to find evidences.

The system consists of cooperative components of an accelerometer, microcontroller unit, GPS device, Global positioning system for Mobile module, sensors for sending a short massage. An accelerometer is applied for awareness and fall detection indicating an accident. If any accident is occurred then the location of the vehicle is traced by the longitude and latitude values of GPS and sends a SMS to the nearest hospitals and family members so that they can be ready for the treatment.

2.2 Existing system

In existing system most of the people associate black boxes with airplanes but they are no longer just the key tool in investigation of airplane accidents. Presently tracking system is introduced in vehicles to avoid the accidents and save peoples life. But these systems are still installed in some of the high-end motorcycles only because these systems are too expensive for most of the motorcycle riders. In our project we are introducing fall detection and alarm system which is expected to save peoples life by detecting the accidents occurred and provides help by tracing the location of the motorcycle riders with the help of GPS technology. This provides the information of the motorcycle rider if any accident is occurred to the family members and at the same time it sends a message to the nearest hospital for the help.

2.3 Design of proposed hardware system

The process of working of this project is explained as follows. The total equipment of this project is placed inside a vehicle is not visible to others. Here we have MEMS accelerometer which will sense the movements of the vehicle continuously. When an accident occurs to the vehicle the movement of the vehicle while the incident is occurring will be detected by the MEMS and this information is given to microcontroller. Here we use GPS module to track the location of the vehicle where the accident has occurred. GPS can get the graphical location of the vehicle and these location values are displayed on the LCD (Liquid Crystal Display). Figure.2. Block diagram of hardware system The location values are given to microcontroller. Controller gives this information to GSM module. By using GSM we can send the message to family members, emergency medical service and nearest hospital.

CHAPTER 3

HARDWARE REQUIREMENTS

HARDWARE COMPONENTS FOR WIRELESS BACKBOX:

- POWER SUPPLY

- TRANSFORMER (230 – 12 V AC)

- VOLTAGE REGULATOR (LM 7805)

- RECTIFIER

- FILTER

- LPC 2148 MICROCONTROLLER

- GSM MODULE

- GPS MODULE

- PUSH BUTTON

- 1N4007

- LED

- LCD

- RESISTOR

- CAPACITOR

- GPS

- LCD

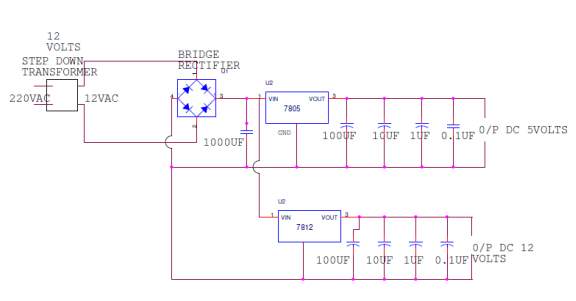

Figure.3(a):Power supply circuit for wireless blackbox

3.2 TRANSFORMER:

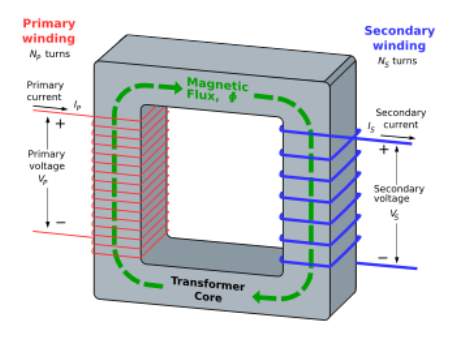

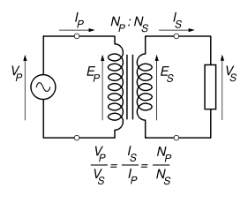

A transformer is a device that transfers electrical energy from one circuit to another through inductively coupled electrical conductors. A changing current in the first circuit (the primary) creates a changing magnetic field; in turn, this magnetic field induces a changing voltage in the second circuit (the secondary). By adding a load to the secondary circuit, one can make current flow in the transformer, thus transferring energy from one circuit to the other.

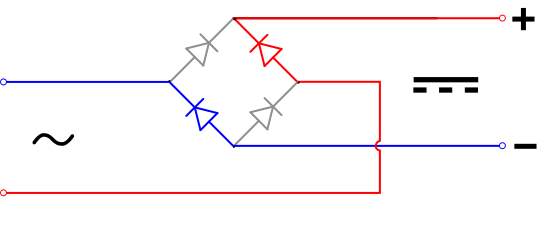

The secondary induced voltage VS, of an ideal transformer, is scaled from the primary VP by a factor equal to the ratio of the number of turns of wire in their respective windings:

Figure.3(a):Power supply circuit for wireless blackbox

3.2 TRANSFORMER:

A transformer is a device that transfers electrical energy from one circuit to another through inductively coupled electrical conductors. A changing current in the first circuit (the primary) creates a changing magnetic field; in turn, this magnetic field induces a changing voltage in the second circuit (the secondary). By adding a load to the secondary circuit, one can make current flow in the transformer, thus transferring energy from one circuit to the other.

The secondary induced voltage VS, of an ideal transformer, is scaled from the primary VP by a factor equal to the ratio of the number of turns of wire in their respective windings:

The transformer is based on two principles: firstly, that an electric current can produce a magnetic field (electromagnetism) and secondly that a changing magnetic field within a coil of wire induces a voltage across the ends of the coil (electromagnetic induction). By changing the current in the primary coil, it changes the strength of its magnetic field; since the changing magnetic field extends into the secondary coil, a voltage is induced across the secondary.

A simplified transformer design is shown below. A current passing through the primary coil creates a magnetic field. The primary and secondary coils are wrapped around a core of very high magnetic permeability, such as iron; this ensures that most of the magnetic field lines produced by the primary current are within the iron and pass through the secondary coil as well as the primary coil.

The transformer is based on two principles: firstly, that an electric current can produce a magnetic field (electromagnetism) and secondly that a changing magnetic field within a coil of wire induces a voltage across the ends of the coil (electromagnetic induction). By changing the current in the primary coil, it changes the strength of its magnetic field; since the changing magnetic field extends into the secondary coil, a voltage is induced across the secondary.

A simplified transformer design is shown below. A current passing through the primary coil creates a magnetic field. The primary and secondary coils are wrapped around a core of very high magnetic permeability, such as iron; this ensures that most of the magnetic field lines produced by the primary current are within the iron and pass through the secondary coil as well as the primary coil.

Fig.3(b):An ideal step-down transformer showing magnetic flux in the core

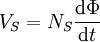

Induction law:The voltage induced across the secondary coil may be calculated from Faraday's law of induction, which states that:

Fig.3(b):An ideal step-down transformer showing magnetic flux in the core

Induction law:The voltage induced across the secondary coil may be calculated from Faraday's law of induction, which states that:

Where VS is the instantaneous voltage, NS is the number of turns in the secondary coil and Φ equals the magnetic flux through one turn of the coil. If the turns of the coil are oriented perpendicular to the magnetic field lines, the flux is the product of the magnetic field strength B and the area A through which it cuts. The area is constant, being equal to the cross-sectional area of the transformer core, whereas the magnetic field varies with time according to the excitation of the primary. Since the same magnetic flux passes through both the primary and secondary coils in an ideal transformer, the instantaneous voltage across the primary winding equals

Where VS is the instantaneous voltage, NS is the number of turns in the secondary coil and Φ equals the magnetic flux through one turn of the coil. If the turns of the coil are oriented perpendicular to the magnetic field lines, the flux is the product of the magnetic field strength B and the area A through which it cuts. The area is constant, being equal to the cross-sectional area of the transformer core, whereas the magnetic field varies with time according to the excitation of the primary. Since the same magnetic flux passes through both the primary and secondary coils in an ideal transformer, the instantaneous voltage across the primary winding equals

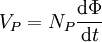

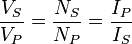

Taking the ratio of the two equations for VS and VP gives the basic equationfor stepping up or stepping down the voltage

Taking the ratio of the two equations for VS and VP gives the basic equationfor stepping up or stepping down the voltage

If the secondary coil is attached to a load that allows current to flow, electrical power is transmitted from the primary circuit to the secondary circuit. Ideally, the transformer is perfectly efficient; all the incoming energy is transformed from the primary circuit to the magnetic field and into the secondary circuit. If this condition is met, the incoming electric power must equal the outgoing power.

Pincoming = IPVP = Poutgoing = ISgiving the ideal transformer equation

If the secondary coil is attached to a load that allows current to flow, electrical power is transmitted from the primary circuit to the secondary circuit. Ideally, the transformer is perfectly efficient; all the incoming energy is transformed from the primary circuit to the magnetic field and into the secondary circuit. If this condition is met, the incoming electric power must equal the outgoing power.

Pincoming = IPVP = Poutgoing = ISgiving the ideal transformer equation

Fig.3(c):Transformer Circuit

Pin-coming = IPVP = Pout-going = ISVS

giving the ideal transformer equation

Fig.3(c):Transformer Circuit

Pin-coming = IPVP = Pout-going = ISVS

giving the ideal transformer equation

If the voltage is increased (stepped up) (VS>VP), then the current is decreased (stepped down) (IS<IP) by the same factor. Transformers are efficient so this formula is a reasonable approximation.

If the voltage is increased (stepped up) (VS>VP), then the current is decreased (stepped down) (IS<IP) by the same factor. Transformers are efficient so this formula is a reasonable approximation.

The impedance in one circuit is transformed by the square of the turns ratio. For example, if an impedance ZS is attached across the terminals of the secondary coil, it appears to the primary circuit to have an impedance of

If the voltage is increased (stepped up) (VS>VP), then the current is decreased (stepped down) (IS<IP) by the same factor. Transformers are efficient so this formula is a reasonable approximation.

If the voltage is increased (stepped up) (VS>VP), then the current is decreased (stepped down) (IS<IP) by the same factor. Transformers are efficient so this formula is a reasonable approximation.

The impedance in one circuit is transformed by the square of the turns ratio. For example, if an impedance ZS is attached across the terminals of the secondary coil, it appears to the primary circuit to have an impedance of

This relationship is reciprocal, so that the impedance ZP of the primary circuit appears to the secondary to be

This relationship is reciprocal, so that the impedance ZP of the primary circuit appears to the secondary to be

Detailed operation:

The simplified description above neglects several practical factors, in particular the primary current required to establish a magnetic field in the core, and the contribution to the field due to current in the secondary circuit.

Models of an ideal transformer typically assume a core of negligible reluctance with two windings of zero resistance. When a voltage is applied to the primary winding, a small current flows, driving flux around the magnetic circuit of the core. The current required to create the flux is termed the magnetizing current; since the ideal core has been assumed to have near-zero reluctance, the magnetizing current is negligible, although still required to create the magnetic field.

The changing magnetic field induces an electromotive force (EMF) across each winding. Since the ideal windings have no impedance, they have no associated voltage drop, and so the voltages VP and VS measured at the terminals of the transformer, are equal to the corresponding EMFs. The primary EMF, acting as it does in opposition to the primary voltage, is sometimes termed the "back EMF". This is due to Lenz's law which states that the induction of EMF would always be such that it will oppose development of any such change in magnetic field

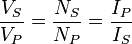

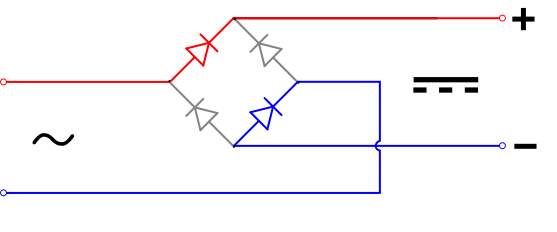

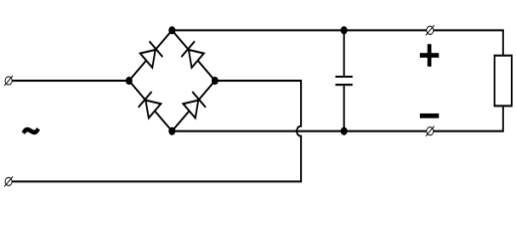

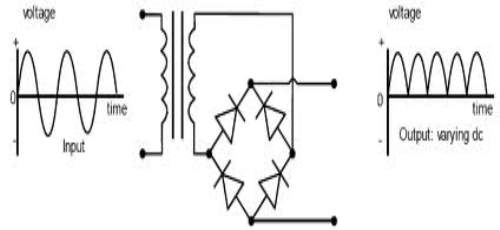

3.3 BRIDGE RECTIFIER

A diode bridge or bridge rectifier is an arrangement of four diodes in a bridge configuration that provides the same polarity of output voltage for any polarity of input voltage. When used in its most common application, for conversion of alternating current (AC) input into direct current (DC) output, it is known as a bridge rectifier. A bridge rectifier provides full-wave rectification from a two-wire AC input, resulting in lower cost and weight as compared to a center-tapped transformer design, but has two diode drops rather than one, thus exhibiting reduced efficiency over a center-tapped design for the same output voltage.

Basic Operation:

When the input connected at the left corner of the diamond is positive with respect to the one connected at the right hand corner, current flows to the right along the upper colored path to the output, and returns to the input supply via the lower one.

Detailed operation:

The simplified description above neglects several practical factors, in particular the primary current required to establish a magnetic field in the core, and the contribution to the field due to current in the secondary circuit.

Models of an ideal transformer typically assume a core of negligible reluctance with two windings of zero resistance. When a voltage is applied to the primary winding, a small current flows, driving flux around the magnetic circuit of the core. The current required to create the flux is termed the magnetizing current; since the ideal core has been assumed to have near-zero reluctance, the magnetizing current is negligible, although still required to create the magnetic field.

The changing magnetic field induces an electromotive force (EMF) across each winding. Since the ideal windings have no impedance, they have no associated voltage drop, and so the voltages VP and VS measured at the terminals of the transformer, are equal to the corresponding EMFs. The primary EMF, acting as it does in opposition to the primary voltage, is sometimes termed the "back EMF". This is due to Lenz's law which states that the induction of EMF would always be such that it will oppose development of any such change in magnetic field

3.3 BRIDGE RECTIFIER

A diode bridge or bridge rectifier is an arrangement of four diodes in a bridge configuration that provides the same polarity of output voltage for any polarity of input voltage. When used in its most common application, for conversion of alternating current (AC) input into direct current (DC) output, it is known as a bridge rectifier. A bridge rectifier provides full-wave rectification from a two-wire AC input, resulting in lower cost and weight as compared to a center-tapped transformer design, but has two diode drops rather than one, thus exhibiting reduced efficiency over a center-tapped design for the same output voltage.

Basic Operation:

When the input connected at the left corner of the diamond is positive with respect to the one connected at the right hand corner, current flows to the right along the upper colored path to the output, and returns to the input supply via the lower one.

Fig.3(d):Bridge Rectifier Circuit

When the right hand corner is positive relative to the left hand corner, current flows along the upper colored path and returns to the supply via the lower colored path.

Fig.3(d):Bridge Rectifier Circuit

When the right hand corner is positive relative to the left hand corner, current flows along the upper colored path and returns to the supply via the lower colored path.

Fig.3(e):Bridge Rectifier Circuit(Right Terminal Positive)

In each case, the upper right output remains positive with respect to the lower right one. Since this is true whether the input is AC or DC, this circuit not only produces DC power when supplied with AC power: it also can provide what is sometimes called "reverse polarity protection". That is, it permits normal functioning when batteries are installed backwards or DC input-power supply wiring "has its wires crossed" (and protects the circuitry it powers against damage that might occur without this circuit in place).

Prior to availability of integrated electronics, such a bridge rectifier was always constructed from discrete components. Since about 1950, a single four-terminal component containing the four diodes connected in the bridge configuration became a standard commercial component and is now available with various voltage and current ratings.

Fig.3(e):Bridge Rectifier Circuit(Right Terminal Positive)

In each case, the upper right output remains positive with respect to the lower right one. Since this is true whether the input is AC or DC, this circuit not only produces DC power when supplied with AC power: it also can provide what is sometimes called "reverse polarity protection". That is, it permits normal functioning when batteries are installed backwards or DC input-power supply wiring "has its wires crossed" (and protects the circuitry it powers against damage that might occur without this circuit in place).

Prior to availability of integrated electronics, such a bridge rectifier was always constructed from discrete components. Since about 1950, a single four-terminal component containing the four diodes connected in the bridge configuration became a standard commercial component and is now available with various voltage and current ratings.

Fig.3(f):Bridge Rectifier Analysis

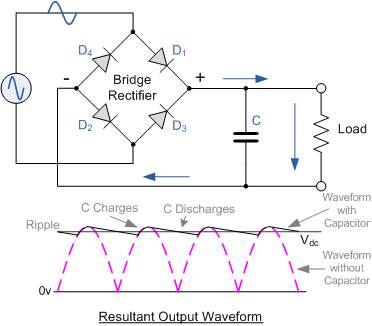

Output smoothing (Using Capacitor)

For many applications, especially with single phase AC where the full-wave bridge serves to convert an AC input into a DC output, the addition of a capacitor may be important because the bridge alone supplies an output voltage of fixed polarity but pulsating magnitude (see diagram above).

Fig.3(f):Bridge Rectifier Analysis

Output smoothing (Using Capacitor)

For many applications, especially with single phase AC where the full-wave bridge serves to convert an AC input into a DC output, the addition of a capacitor may be important because the bridge alone supplies an output voltage of fixed polarity but pulsating magnitude (see diagram above).

Fig.3(g):Bridge Rectifier with Output voltage

The function of this capacitor, known as a reservoir capacitor (aka smoothing capacitor) is to lessen the variation in (or 'smooth') the rectified AC output voltage waveform from the bridge. One explanation of 'smoothing' is that the capacitor provides a low impedance path to the AC component of the output, reducing the AC voltage across, and AC current through, the resistive load. In less technical terms, any drop in the output voltage and current of the bridge tends to be cancelled by loss of charge in the capacitor.

This charge flows out as additional current through the load. Thus the change of load current and voltage is reduced relative to what would occur without the capacitor. Increases of voltage correspondingly store excess charge in the capacitor, thus moderating the change in output voltage / current. Also see rectifier output smoothing.

The simplified circuit shown has a well deserved reputation for being dangerous, because, in some applications, the capacitor can retain a lethal charge after the AC power source is removed. If supplying a dangerous voltage, a practical circuit should include a reliable way to safely discharge the capacitor. If the normal load can not be guaranteed to perform this function, perhaps because it can be disconnected, the circuit should include a bleeder resistor connected as close as practical across the capacitor. This resistor should consume a current large enough to discharge the capacitor in a reasonable time, but small enough to avoid unnecessary power waste.

Because a bleeder sets a minimum current drain, the regulation of the circuit, defined as percentage voltage change from minimum to maximum load, is improved. However in many cases the improvement is of insignificant magnitude.

The capacitor and the load resistance have a typical time constant τ = RC where C and R are the capacitance and load resistance respectively. As long as the load resistor is large enough so that this time constant is much longer than the time of one ripple cycle, the above configuration will produce a smoothed DC voltage across the load.

In some designs, a series resistor at the load side of the capacitor is added. The smoothing can then be improved by adding additional stages of capacitor–resistor pairs, often done only for sub-supplies to critical high-gain circuits that tend to be sensitive to supply voltage noise.

The idealized waveforms shown above are seen for both voltage and current when the load on the bridge is resistive. When the load includes a smoothing capacitor, both the voltage and the current waveforms will be greatly changed. While the voltage is smoothed, as described above, current will flow through the bridge only during the time when the input voltage is greater than the capacitor voltage. For example, if the load draws an average current of n Amps, and the diodes conduct for 10% of the time, the average diode current during conduction must be 10n Amps. This non-sinusoidal current leads to harmonic distortion and a poor power factor in the AC supply.

In a practical circuit, when a capacitor is directly connected to the output of a bridge, the bridge diodes must be sized to withstand the current surge that occurs when the power is turned on at the peak of the AC voltage and the capacitor is fully discharged. Sometimes a small series resistor is included before the capacitor to limit this current, though in most applications the power supply transformer's resistance is already sufficient.

Output can also be smoothed using a choke and second capacitor. The choke tends to keep the current (rather than the voltage) more constant. Due to the relatively high cost of an effective choke compared to a resistor and capacitor this is not employed in modern equipment.

Some early console radios created the speaker's constant field with the current from the high voltage ("B +") power supply, which was then routed to the consuming circuits, (permanent magnets were considered too weak for good performance) to create the speaker's constant magnetic field. The speaker field coil thus performed 2 jobs in one: it acted as a choke, filtering the power supply, and it produced the magnetic field to operate the speaker.

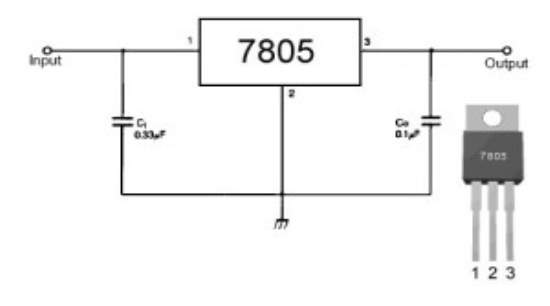

3.4 VOLTAGE REGULATOR 7805

Features

• Output Current up to 1A.

• Output Voltages of 5, 6, 8, 9, 10, 12, 15, 18, 24V.

• Thermal Overload Protection.

• Short Circuit Protection.

• Output Transistor Safe Operating Area Protection.

Fig.3(g):Bridge Rectifier with Output voltage

The function of this capacitor, known as a reservoir capacitor (aka smoothing capacitor) is to lessen the variation in (or 'smooth') the rectified AC output voltage waveform from the bridge. One explanation of 'smoothing' is that the capacitor provides a low impedance path to the AC component of the output, reducing the AC voltage across, and AC current through, the resistive load. In less technical terms, any drop in the output voltage and current of the bridge tends to be cancelled by loss of charge in the capacitor.

This charge flows out as additional current through the load. Thus the change of load current and voltage is reduced relative to what would occur without the capacitor. Increases of voltage correspondingly store excess charge in the capacitor, thus moderating the change in output voltage / current. Also see rectifier output smoothing.

The simplified circuit shown has a well deserved reputation for being dangerous, because, in some applications, the capacitor can retain a lethal charge after the AC power source is removed. If supplying a dangerous voltage, a practical circuit should include a reliable way to safely discharge the capacitor. If the normal load can not be guaranteed to perform this function, perhaps because it can be disconnected, the circuit should include a bleeder resistor connected as close as practical across the capacitor. This resistor should consume a current large enough to discharge the capacitor in a reasonable time, but small enough to avoid unnecessary power waste.

Because a bleeder sets a minimum current drain, the regulation of the circuit, defined as percentage voltage change from minimum to maximum load, is improved. However in many cases the improvement is of insignificant magnitude.

The capacitor and the load resistance have a typical time constant τ = RC where C and R are the capacitance and load resistance respectively. As long as the load resistor is large enough so that this time constant is much longer than the time of one ripple cycle, the above configuration will produce a smoothed DC voltage across the load.

In some designs, a series resistor at the load side of the capacitor is added. The smoothing can then be improved by adding additional stages of capacitor–resistor pairs, often done only for sub-supplies to critical high-gain circuits that tend to be sensitive to supply voltage noise.

The idealized waveforms shown above are seen for both voltage and current when the load on the bridge is resistive. When the load includes a smoothing capacitor, both the voltage and the current waveforms will be greatly changed. While the voltage is smoothed, as described above, current will flow through the bridge only during the time when the input voltage is greater than the capacitor voltage. For example, if the load draws an average current of n Amps, and the diodes conduct for 10% of the time, the average diode current during conduction must be 10n Amps. This non-sinusoidal current leads to harmonic distortion and a poor power factor in the AC supply.

In a practical circuit, when a capacitor is directly connected to the output of a bridge, the bridge diodes must be sized to withstand the current surge that occurs when the power is turned on at the peak of the AC voltage and the capacitor is fully discharged. Sometimes a small series resistor is included before the capacitor to limit this current, though in most applications the power supply transformer's resistance is already sufficient.

Output can also be smoothed using a choke and second capacitor. The choke tends to keep the current (rather than the voltage) more constant. Due to the relatively high cost of an effective choke compared to a resistor and capacitor this is not employed in modern equipment.

Some early console radios created the speaker's constant field with the current from the high voltage ("B +") power supply, which was then routed to the consuming circuits, (permanent magnets were considered too weak for good performance) to create the speaker's constant magnetic field. The speaker field coil thus performed 2 jobs in one: it acted as a choke, filtering the power supply, and it produced the magnetic field to operate the speaker.

3.4 VOLTAGE REGULATOR 7805

Features

• Output Current up to 1A.

• Output Voltages of 5, 6, 8, 9, 10, 12, 15, 18, 24V.

• Thermal Overload Protection.

• Short Circuit Protection.

• Output Transistor Safe Operating Area Protection.

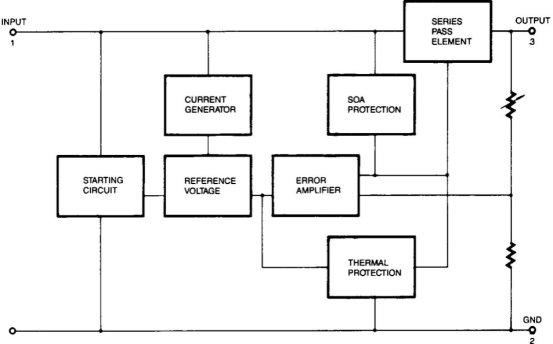

Fig.3(h):Voltage Regulator Circuit

Description

The LM78XX/LM78XXA series of three-terminal positive regulators are available in the TO-220/D-PAK package and with several fixed output voltages, making them useful in a Wide range of applications. Each type employs internal current limiting, thermal shutdown and safe operating area protection, making it essentially indestructible. If adequate heat sinking is provided, they can deliver over 1A output Current. Although designed primarily as fixed voltage regulators, these devices can be used with external components to obtain adjustable voltages and currents.

Fig.3(h):Voltage Regulator Circuit

Description

The LM78XX/LM78XXA series of three-terminal positive regulators are available in the TO-220/D-PAK package and with several fixed output voltages, making them useful in a Wide range of applications. Each type employs internal current limiting, thermal shutdown and safe operating area protection, making it essentially indestructible. If adequate heat sinking is provided, they can deliver over 1A output Current. Although designed primarily as fixed voltage regulators, these devices can be used with external components to obtain adjustable voltages and currents.

Fig.3(i):Block diagram of voltage regulator

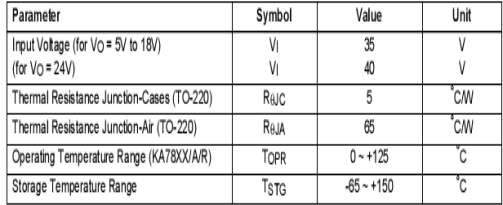

TABLE 3(a):Ratings of the voltage regulator

Fig.3(i):Block diagram of voltage regulator

TABLE 3(a):Ratings of the voltage regulator

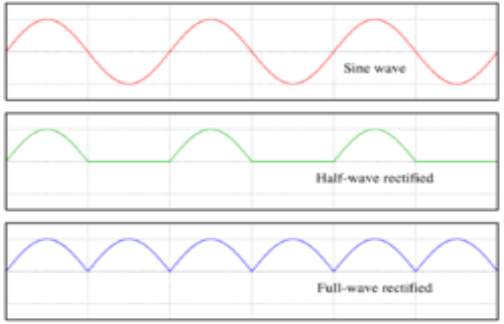

3.5 RECTIFIER

A rectifier is an electrical device that converts alternating current (AC), which periodically reverses direction, to direct current (DC), current that flows in only one direction, a process known as rectification. Rectifiers have many uses including as components of power supplies and as detectors of radio signals. Rectifiers may be made of solid statediodes, vacuum tube diodes, mercury arc valves, and other components. The output from the transformer is fed to the rectifier. It converts A.C. into pulsating D.C. The rectifier may be a half wave or a full wave rectifier. In this project, a bridge rectifier is used because of its merits like good stability and full wave rectification. In positive half cycleonly two diodes( 1 set of parallel diodes) will conduct, in negative half cycle remaining two diodes will conduct and they will conduct only in forward bias only.

3.5 RECTIFIER

A rectifier is an electrical device that converts alternating current (AC), which periodically reverses direction, to direct current (DC), current that flows in only one direction, a process known as rectification. Rectifiers have many uses including as components of power supplies and as detectors of radio signals. Rectifiers may be made of solid statediodes, vacuum tube diodes, mercury arc valves, and other components. The output from the transformer is fed to the rectifier. It converts A.C. into pulsating D.C. The rectifier may be a half wave or a full wave rectifier. In this project, a bridge rectifier is used because of its merits like good stability and full wave rectification. In positive half cycleonly two diodes( 1 set of parallel diodes) will conduct, in negative half cycle remaining two diodes will conduct and they will conduct only in forward bias only.

Fig.3(j):Full Wave Rectifier

3.6 FILTER

Capacitive filter is used in this project. It removes the ripples from the output of rectifier and smoothens the D.C. Output received from this filter is constant until the mains voltage and load is maintained constant. However, if either of the two is varied, D.C. voltage received at this point changes. Therefore a regulator is applied at the output stage.

The simple capacitor filter is the most basic type of power supply filter. The use of this filter is very limited. It is sometimes used on extremely high-voltage, low-current power supplies for cathode-ray and similar electron tubes that require very little load current from the supply. This filter is also used in circuits where the power-supply ripple frequency is not critical and can be relatively high. Below figure can show how the capacitor changes and discharges.

Fig.3(j):Full Wave Rectifier

3.6 FILTER

Capacitive filter is used in this project. It removes the ripples from the output of rectifier and smoothens the D.C. Output received from this filter is constant until the mains voltage and load is maintained constant. However, if either of the two is varied, D.C. voltage received at this point changes. Therefore a regulator is applied at the output stage.

The simple capacitor filter is the most basic type of power supply filter. The use of this filter is very limited. It is sometimes used on extremely high-voltage, low-current power supplies for cathode-ray and similar electron tubes that require very little load current from the supply. This filter is also used in circuits where the power-supply ripple frequency is not critical and can be relatively high. Below figure can show how the capacitor changes and discharges.

Fig.3(k):output waveform from filter

3.7 LPC 2148 ARM MICROCONTROLLER

3.7.1GENERAL DESCRIPTION OF LPC 2148:

The LPC2148 microcontrollers are based on a 16-bit/32-bit ARM7TDMI-CPU with real-time emulation and embedded trace support, that combine microcontroller with embedded high speed flash memory ranging from 32 kB to 512 kB. A 128-bit wide memory interface and unique accelerator architecture enable 32-bit code execution at the maximum clock rate. For critical code size applications, the alternative 16-bit Thumb mode reduces code by more than 30 % with minimal performance penalty. Due to their tiny size and low power consumption, LPC2148 are ideal for applications where miniaturization is a key requirement, such as access control and point-of-sale. Serial communications interfaces ranging from a USB 2.0 Full-speed device, multiple UARTs, SPI, SSP to I2C-bus and on-chip SRAM of 8 kB up to 40 kB, make these devices very well suited for communication gateways and protocol converters, soft modems, voice recognition and low end imaging, providing both large buffer size and high processing power. Various 32-bit timers, single or dual 10-bit ADC(s), 10-bit DAC, PWM channels and 45 fast GPIO lines with up to nine edge or level sensitive external interrupt pins make these microcontrollers suitable for industrial control and medical systems.

Key features:

16-bit/32-bit ARM7TDMI-S microcontroller in a tiny LQFP64 package.8 kB to 40 kB of on-chip static RAM and 32 kB to 512 kB of on-chip flash memory.128-bit wide interface/accelerator enables high-speed 60 MHz operation.In-System Programming/In-Application Programming (ISP/IAP) via on-chip boot loaderSoftware. Single flash sector or full chip erase in 400 ms and programming of256 bytes in 1 ms.Embedded ICE RT and Embedded Trace interfaces offer real-time debugging with the On-chip Real Monitor software and high-speed tracing of instruction execution.USB 2.0 Full-speed compliant device controller with 2 kB of endpoint RAM.Inaddition,the LPC2146/48 provides 8 kB of on-chip RAM accessible to USB by DMA.One or two (LPC2141/42 vs. LPC2144/46/48) 10-bit ADCs provide a total of 6/14 analog inputs, with conversion times as low as 2.44 μs per channel.Single 10-bit DAC provides variable analog output (LPC2142/44/46/48 only). Two 32-bit timers/external event counters (with four capture and four compare Vectored Interrupt Controller (VIC) with configurable priorities and vector addresses.Up to 45 of 5 V tolerant fast general purpose I/O pins in a tiny LQFP64 package. Up to 21 external interrupt pins available.60 MHz maximum CPU clock available from programmable on-chip PLL with settling Time of 100 μs.On-chip integrated oscillator operates with an external crystal from 1 MHz to 25 MHz.Power saving modes include Idle and Power-down.Individual enable/disable of peripheral functions as well as peripheral clock scaling for Additional power optimization.Processor wake-up from Power-down mode via external interrupt or BOD.

Fig.3(k):output waveform from filter

3.7 LPC 2148 ARM MICROCONTROLLER

3.7.1GENERAL DESCRIPTION OF LPC 2148:

The LPC2148 microcontrollers are based on a 16-bit/32-bit ARM7TDMI-CPU with real-time emulation and embedded trace support, that combine microcontroller with embedded high speed flash memory ranging from 32 kB to 512 kB. A 128-bit wide memory interface and unique accelerator architecture enable 32-bit code execution at the maximum clock rate. For critical code size applications, the alternative 16-bit Thumb mode reduces code by more than 30 % with minimal performance penalty. Due to their tiny size and low power consumption, LPC2148 are ideal for applications where miniaturization is a key requirement, such as access control and point-of-sale. Serial communications interfaces ranging from a USB 2.0 Full-speed device, multiple UARTs, SPI, SSP to I2C-bus and on-chip SRAM of 8 kB up to 40 kB, make these devices very well suited for communication gateways and protocol converters, soft modems, voice recognition and low end imaging, providing both large buffer size and high processing power. Various 32-bit timers, single or dual 10-bit ADC(s), 10-bit DAC, PWM channels and 45 fast GPIO lines with up to nine edge or level sensitive external interrupt pins make these microcontrollers suitable for industrial control and medical systems.

Key features:

16-bit/32-bit ARM7TDMI-S microcontroller in a tiny LQFP64 package.8 kB to 40 kB of on-chip static RAM and 32 kB to 512 kB of on-chip flash memory.128-bit wide interface/accelerator enables high-speed 60 MHz operation.In-System Programming/In-Application Programming (ISP/IAP) via on-chip boot loaderSoftware. Single flash sector or full chip erase in 400 ms and programming of256 bytes in 1 ms.Embedded ICE RT and Embedded Trace interfaces offer real-time debugging with the On-chip Real Monitor software and high-speed tracing of instruction execution.USB 2.0 Full-speed compliant device controller with 2 kB of endpoint RAM.Inaddition,the LPC2146/48 provides 8 kB of on-chip RAM accessible to USB by DMA.One or two (LPC2141/42 vs. LPC2144/46/48) 10-bit ADCs provide a total of 6/14 analog inputs, with conversion times as low as 2.44 μs per channel.Single 10-bit DAC provides variable analog output (LPC2142/44/46/48 only). Two 32-bit timers/external event counters (with four capture and four compare Vectored Interrupt Controller (VIC) with configurable priorities and vector addresses.Up to 45 of 5 V tolerant fast general purpose I/O pins in a tiny LQFP64 package. Up to 21 external interrupt pins available.60 MHz maximum CPU clock available from programmable on-chip PLL with settling Time of 100 μs.On-chip integrated oscillator operates with an external crystal from 1 MHz to 25 MHz.Power saving modes include Idle and Power-down.Individual enable/disable of peripheral functions as well as peripheral clock scaling for Additional power optimization.Processor wake-up from Power-down mode via external interrupt or BOD.

Fig.3(l):pin diagram of LPC 2148

Fig.3(l):pin diagram of LPC 2148

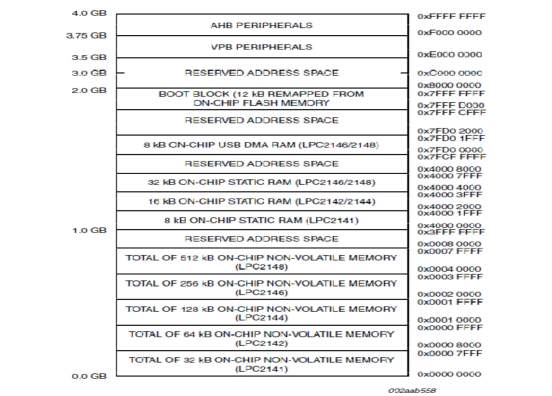

The LPC2148 memory map incorporates several distinct regions, as shown in Fig 4.2 In addition, the CPU interrupt vectors may be remapped to allow them to reside in either flash memory (the default) or on-chip static RAM.

Fig.3(m):Memorymap

The LPC2148 memory map incorporates several distinct regions, as shown in Fig 4.2 In addition, the CPU interrupt vectors may be remapped to allow them to reside in either flash memory (the default) or on-chip static RAM.

Fig.3(m):Memorymap

- Interrupt Sources

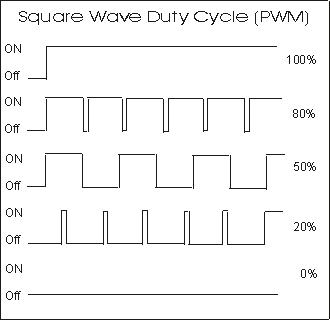

Fig. 3.(n):Duty Cycles of PWM

3.8.6 Power Delivery

PWM can be used to adjust the total amount of power delivered to a load without losses normally incurred when a power transfer is limited by resistive means. The drawbacks are the pulsations defined by the duty cycle, switching frequency and properties of the load. With a sufficiently high switching frequency and, when necessary, using additional passive electronic filters the pulse train can be smoothed and average analog waveform recovered.

High frequency PWM power control systems are easily realisable with semiconductor switches. As has been already stated above almost no power is dissipated by the switch in either on or off state. However, during the transitions between on and off states both voltage and current are non-zero and thus considerable power is dissipated in the switches. Luckily, the change of state between fully on and fully off is quite rapid (typically less than 100 nanoseconds) relative to typical on or

off times, and so the average power dissipation is quite low compared to the power being delivered even when high switching frequencies are used.

Modern semiconductor switches such as MOSFETs or Insulated-gate bipolar transistors (IGBTs) are quite ideal components. Thus high efficiency controllers can be built. Typically frequency converters used to control AC motors have efficiency that is better than 98 %. Switching power supplies have lower efficiency due to low output voltage levels (often even less than 2 V for microprocessors are needed) but still more than 70-80 % efficiency can be achieved. Variable-speed fan controllers for computers usually use PWM, as it is far more efficient when compared to a potentiometer or rheostat. (Neither of the latter is practical to operate electronically; they would require a small drive motor).

Light dimmers for home use employ a specific type of PWM control. Home use light dimmers typically include electronic circuitry which suppresses current flow during defined portions of each cycle of the AC line voltage. Adjusting the brightness of light emitted by a light source is then merely a matter of setting at what voltage (or phase) in the AC half cycle the dimmer begins to provide electrical current to the light source. In this case the PWM duty cycle is the ratio of the conduction time to the duration of the half AC cycle defined by the frequency of the AC line voltage.

3.8.7 Pulse Width Modulation (PWM) in ARM LPC2148

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC2141/2/4/6/8. The Timer is designed to count cycles of the peripheral clock (PCLK) and optionally generate interrupts or perform other actions when specified timer values occur, based on seven match registers. It also includes four capture inputs to save the timer value when an input signal transitions, and optionally generate an interrupt when those events occur. The PWM function is in addition to these features, and is based on match register events.The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

Two match registers can be used to provide a single edge controlled PWM output. One match register (PWMMR0) controls the PWM cycle rate, by resetting the

count upon match. The other match register controls the PWM edge position. Additional single edge controlled PWM outputs require only one match register each, since the repetition rate is the same for all PWM outputs. Multiple single edge controlled PWM outputs will all have a rising edge at the beginning of each PWM cycle, when an PWMMR0 match occurs.

Three match registers can be used to provide a PWM output with both edges controlled. Again, the PWMMR0 match register controls the PWM cycle rate. The other match registers control the two PWM edge positions. Additional double edge controlled PWM outputs require only two match registers each, since the repetition rate is the same for all PWM outputs.

With double edge controlled PWM outputs, specific match registers control the rising and falling edge of the output. This allows both positive going PWM pulses (when the rising edge occurs prior to the falling edge), and negative going PWM pulses (when the falling edge occurs prior to the rising edge).

Fig. 3.(n):Duty Cycles of PWM

3.8.6 Power Delivery

PWM can be used to adjust the total amount of power delivered to a load without losses normally incurred when a power transfer is limited by resistive means. The drawbacks are the pulsations defined by the duty cycle, switching frequency and properties of the load. With a sufficiently high switching frequency and, when necessary, using additional passive electronic filters the pulse train can be smoothed and average analog waveform recovered.

High frequency PWM power control systems are easily realisable with semiconductor switches. As has been already stated above almost no power is dissipated by the switch in either on or off state. However, during the transitions between on and off states both voltage and current are non-zero and thus considerable power is dissipated in the switches. Luckily, the change of state between fully on and fully off is quite rapid (typically less than 100 nanoseconds) relative to typical on or

off times, and so the average power dissipation is quite low compared to the power being delivered even when high switching frequencies are used.

Modern semiconductor switches such as MOSFETs or Insulated-gate bipolar transistors (IGBTs) are quite ideal components. Thus high efficiency controllers can be built. Typically frequency converters used to control AC motors have efficiency that is better than 98 %. Switching power supplies have lower efficiency due to low output voltage levels (often even less than 2 V for microprocessors are needed) but still more than 70-80 % efficiency can be achieved. Variable-speed fan controllers for computers usually use PWM, as it is far more efficient when compared to a potentiometer or rheostat. (Neither of the latter is practical to operate electronically; they would require a small drive motor).

Light dimmers for home use employ a specific type of PWM control. Home use light dimmers typically include electronic circuitry which suppresses current flow during defined portions of each cycle of the AC line voltage. Adjusting the brightness of light emitted by a light source is then merely a matter of setting at what voltage (or phase) in the AC half cycle the dimmer begins to provide electrical current to the light source. In this case the PWM duty cycle is the ratio of the conduction time to the duration of the half AC cycle defined by the frequency of the AC line voltage.

3.8.7 Pulse Width Modulation (PWM) in ARM LPC2148

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC2141/2/4/6/8. The Timer is designed to count cycles of the peripheral clock (PCLK) and optionally generate interrupts or perform other actions when specified timer values occur, based on seven match registers. It also includes four capture inputs to save the timer value when an input signal transitions, and optionally generate an interrupt when those events occur. The PWM function is in addition to these features, and is based on match register events.The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

Two match registers can be used to provide a single edge controlled PWM output. One match register (PWMMR0) controls the PWM cycle rate, by resetting the

count upon match. The other match register controls the PWM edge position. Additional single edge controlled PWM outputs require only one match register each, since the repetition rate is the same for all PWM outputs. Multiple single edge controlled PWM outputs will all have a rising edge at the beginning of each PWM cycle, when an PWMMR0 match occurs.

Three match registers can be used to provide a PWM output with both edges controlled. Again, the PWMMR0 match register controls the PWM cycle rate. The other match registers control the two PWM edge positions. Additional double edge controlled PWM outputs require only two match registers each, since the repetition rate is the same for all PWM outputs.

With double edge controlled PWM outputs, specific match registers control the rising and falling edge of the output. This allows both positive going PWM pulses (when the rising edge occurs prior to the falling edge), and negative going PWM pulses (when the falling edge occurs prior to the rising edge).

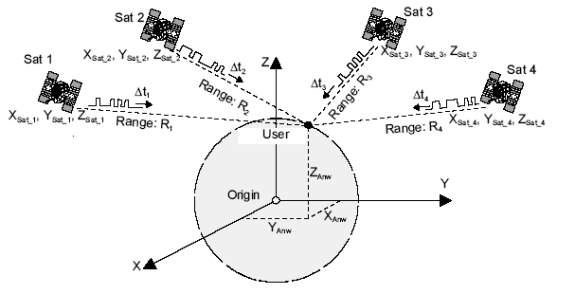

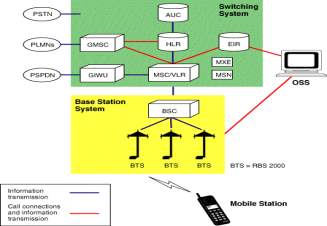

3.9 GLOBAL POSITIONING SYSTEM(GPS)

The Global Positioning System (GPS) is the only fully functional Global Navigation Satellite System (GNSS). The GPS uses a constellation of between 24 and 32 Medium Earth Orbit satellites that transmit precise microwave signals, which enable GPS receivers to determine their location, speed,. GPS was developed by the United States Department of Defense. Its official name is NAVSTAR-GPS. Although NAVSTAR-GPS is not an acronym, a few backronyms have been created for it. The GPS satellite constellation is managed by the United States Air Force 50th Space Wing.

Global Positioning System is an earth-orbiting-satellite based system that provides signals available anywhere on or above the earth, twenty-four hours a day, which can be used to determine precise time and the position of a GPS receiver in three dimensions. GPS is increasingly used as an input for Geographic Information Systems particularly for precise positioning of geospatial data and the collection of data in the field.Precise positioning is possible using GPS receivers at reference locations providing corrections and relative positioning data for remote receivers. Time and frequency dissemination, based on the precise clocks on board the SVs and controlled by the monitor stations, is another, use for GPS. Astronomical observatories telecommunications facilities and laboratory standards can be set to precise time signals or controlled to accurate frequencies by special purpose GPS receivers.

Similar satellite navigation systems include the Russian GLONASS (incomplete as of 2008), the upcoming European Galileo positioning system, the proposed COMPASS navigation system of China, and IRNSS of India.

Following the shooting down of Korean Air Lines Flight 007 in 1983, President Ronald Reagan issued a directive making the system available free for civilian use as a common good. Since then, GPS has become a widely used aid to navigation worldwide, and a useful tool for map-making, land surveying, commerce, scientific uses, and hobbies such as geocaching. GPS also provides a precise time reference used in many applications including scientific study of earthquakes, and synchronization of telecommunications networks.

3.9 GLOBAL POSITIONING SYSTEM(GPS)

The Global Positioning System (GPS) is the only fully functional Global Navigation Satellite System (GNSS). The GPS uses a constellation of between 24 and 32 Medium Earth Orbit satellites that transmit precise microwave signals, which enable GPS receivers to determine their location, speed,. GPS was developed by the United States Department of Defense. Its official name is NAVSTAR-GPS. Although NAVSTAR-GPS is not an acronym, a few backronyms have been created for it. The GPS satellite constellation is managed by the United States Air Force 50th Space Wing.

Global Positioning System is an earth-orbiting-satellite based system that provides signals available anywhere on or above the earth, twenty-four hours a day, which can be used to determine precise time and the position of a GPS receiver in three dimensions. GPS is increasingly used as an input for Geographic Information Systems particularly for precise positioning of geospatial data and the collection of data in the field.Precise positioning is possible using GPS receivers at reference locations providing corrections and relative positioning data for remote receivers. Time and frequency dissemination, based on the precise clocks on board the SVs and controlled by the monitor stations, is another, use for GPS. Astronomical observatories telecommunications facilities and laboratory standards can be set to precise time signals or controlled to accurate frequencies by special purpose GPS receivers.

Similar satellite navigation systems include the Russian GLONASS (incomplete as of 2008), the upcoming European Galileo positioning system, the proposed COMPASS navigation system of China, and IRNSS of India.

Following the shooting down of Korean Air Lines Flight 007 in 1983, President Ronald Reagan issued a directive making the system available free for civilian use as a common good. Since then, GPS has become a widely used aid to navigation worldwide, and a useful tool for map-making, land surveying, commerce, scientific uses, and hobbies such as geocaching. GPS also provides a precise time reference used in many applications including scientific study of earthquakes, and synchronization of telecommunications networks.

Fig 3(o) GPS satellite

Fig 3(o) GPS satellite

3.9.1Basic concept of GPS operation

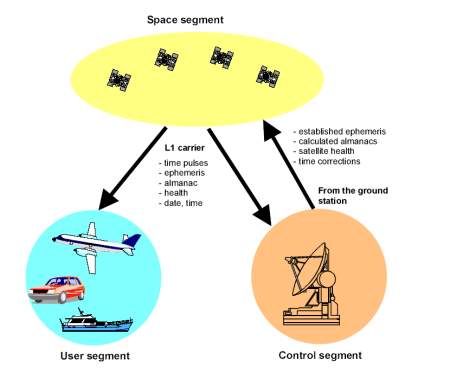

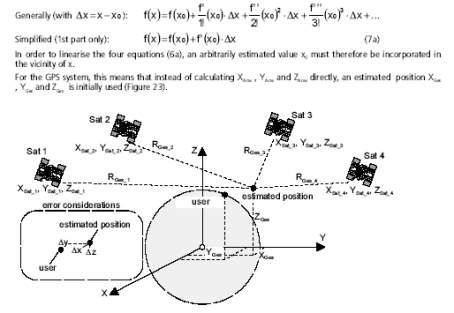

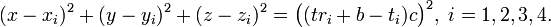

A GPS receiver calculates its position by carefully timing the signals sent by the constellation of GPS satellites high above the Earth. Each satellite continually transmits messages containing the time the message was sent, a precise orbit for the satellite sending the message (the ephemeris), and the general system health and rough orbits of all GPS satellites (the almanac). These signals travel at the speed of light through outer space, and slightly slower through the atmosphere. The receiver uses the arrival time of each message to measure the distance to each satellite, from which it determines the position of the receiver (conceptually the intersection of spheres - see trilateration ) The resulting coordinates are converted to more user-friendly forms such as latitude and longitude, or location on a map, then displayed to the user. It might seem that three satellites would be enough to solve for a position, since space has three dimensions. However, a three satellite solution requires the time be known to a nanosecond or so, far better than any non-laboratory clock can provide. Using four or more satellites allows the receiver to solve for time as well as geographical position, eliminating the need for a super accurate clock. In other words, the receiver uses four measurements to solve for four variables: x, y, z, and t. While many GPS applications have no particular use for this (very accurate) time, it is used in some GPS applications such as time transfer, and it is the only variable of interest in some applications, such as traffic signal timing. Although four satellites are required for normal operation, fewer may be needed in some special cases. If one variable is already known (for example, a ship or plane may already know its altitude), a receiver can determine its position using only three satellites. Also, in practice, receivers use additional clues (Doppler shift of satellite signals, last known position, dead reckoning, inertiral navigation, and so on) to give degraded answers when fewer than four satellites are visible.3.9.2Position calculation introduction

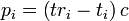

To provide an introductory description of how a GPS receiver works, errors will be ignored in this section. Using messages received from a minimum of four visible satellites, a GPS receiver is able to determine the satellite positions and time sent. The x, y, and z components of position and the time sent are designated as![\left [x_i, y_i, z_i, t_i\right ]](https://images.ukdissertations.com/18/0025970.029.jpg) where the subscript i denotes the satellite number and has the value 1, 2, 3, or 4. Knowing the indicated time the message was received

where the subscript i denotes the satellite number and has the value 1, 2, 3, or 4. Knowing the indicated time the message was received  , the GPS receiver can compute the indicated transit time,

, the GPS receiver can compute the indicated transit time,  . of the message.

Assuming the message traveled at the speed of light, c, the distance travelled,

. of the message.

Assuming the message traveled at the speed of light, c, the distance travelled,  can be computed as

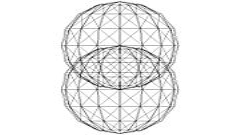

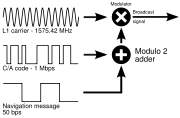

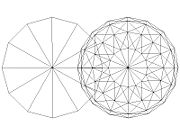

can be computed as  . Knowing the distance from GPS receiver to a satellite and the position of a satellite implies that the GPS receiver is on the surface of a sphere centered at the position of a satellite. Thus we know that the indicated position of the GPS receiver is at or near the intersection of the surfaces of four spheres. In the ideal case of no errors, the GPS receiver will be at an intersection of the surfaces of four spheres. The surfaces of two spheres if they intersect in more than one point intersect in a circle. A figure, two sphere surfaces intersecting in a circle, is shown below.

. Knowing the distance from GPS receiver to a satellite and the position of a satellite implies that the GPS receiver is on the surface of a sphere centered at the position of a satellite. Thus we know that the indicated position of the GPS receiver is at or near the intersection of the surfaces of four spheres. In the ideal case of no errors, the GPS receiver will be at an intersection of the surfaces of four spheres. The surfaces of two spheres if they intersect in more than one point intersect in a circle. A figure, two sphere surfaces intersecting in a circle, is shown below.

Two Sphere Surfaces Intersecting in a Circle

The article, trilateration, shows mathematically that two spheres intersecting in more than one point intersect in a circle.

Two Sphere Surfaces Intersecting in a Circle

The article, trilateration, shows mathematically that two spheres intersecting in more than one point intersect in a circle.

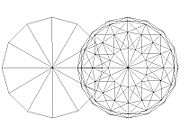

Surface of Sphere Intersecting a Circle (not disk) at Two Points

A circle and sphere surface in most cases of practical interest intersects at two points, although it is conceivable that they could intersect in 0 or 1 point. Another figure, Surface of Sphere Intersecting a Circle (not disk) at Two Points, is shown to aid in visualizing this intersection. Again trilateration clearly show this mathematically. The correct position of the GPS receiver is the one that is closest to the fourth sphere.

Surface of Sphere Intersecting a Circle (not disk) at Two Points

A circle and sphere surface in most cases of practical interest intersects at two points, although it is conceivable that they could intersect in 0 or 1 point. Another figure, Surface of Sphere Intersecting a Circle (not disk) at Two Points, is shown to aid in visualizing this intersection. Again trilateration clearly show this mathematically. The correct position of the GPS receiver is the one that is closest to the fourth sphere.

3.9.3Correcting GPS clock

The method of calculating position for the case of no errors has been explained. One of the most important errors is the error in the GPS receiver clock. Because of the very large value of c, the speed of light, the estimated distances from the GPS receiver to the satellites, the pseudo ranges, are very sensitive to errors in the GPS receiver clock. This seems to suggest that an extremely accurate and expensive clock is required for the GPS receiver to work. On the other hand, manufacturers would like to make an inexpensive GPS receiver which can be mass marketed. The manufacturers were thus faced with a difficult design problem. The technique that solves this problem is based on the way sphere surfaces intersect in the GPS problem. It is likely the surfaces of the three spheres intersect since the circle of intersection of the first two spheres is normally quite large and thus the third sphere surface is likely to intersect this large circle. It is very unlikely that the surface of the sphere corresponding to the fourth satellite will intersect either of the two points of intersection of the first three since any clock error could cause it to miss intersecting a point. However the distance from the valid estimate of GPS receiver position to the surface of the sphere corresponding to the fourth satellite can be used to compute a clock correction. Let denote the distance from the valid estimate of GPS receiver position to the fourth satellite and let

denote the distance from the valid estimate of GPS receiver position to the fourth satellite and let  denote the pseudo range of the fourth satellite. Let

denote the pseudo range of the fourth satellite. Let  . Note that

. Note that  is the distance from the computed GPS receiver position to the surface of the sphere corresponding to the fourth satellite. Thus the quotient,

is the distance from the computed GPS receiver position to the surface of the sphere corresponding to the fourth satellite. Thus the quotient,  , provides an estimate of:

(correct time) - (time indicated by the receiver's on-board clock)

and the GPS receiver clock can be advanced if

, provides an estimate of:

(correct time) - (time indicated by the receiver's on-board clock)

and the GPS receiver clock can be advanced if  is positive or delayed if

is positive or delayed if  is negative.

is negative.

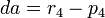

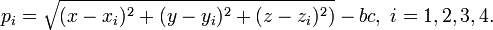

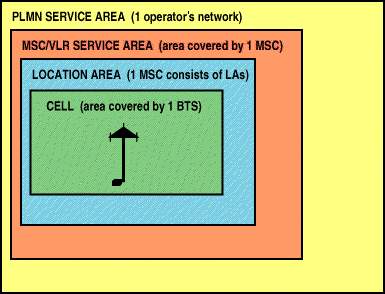

3.9.4System segmentation

The current GPS consists of three major segments. These are the space segment (SS), a control segment (CS), and a user segment (US). 3.9.5Space segment Fig 3(p) GPS Constellation

A visual example of the GPS constellation in motion with the Earth rotating. Notice how the number of satellites in view from a given point on the Earth's surface, in this example at 45°N, changes with time.

The space segment (SS) comprises the orbiting GPS satellites, or Space Vehicles (SV) in GPS parlance. The GPS design originally called for 24 SVs, eight each in three circular orbital planes, but this was modified to six planes with four satellites each. The orbital

Fig 3(p) GPS Constellation

A visual example of the GPS constellation in motion with the Earth rotating. Notice how the number of satellites in view from a given point on the Earth's surface, in this example at 45°N, changes with time.

The space segment (SS) comprises the orbiting GPS satellites, or Space Vehicles (SV) in GPS parlance. The GPS design originally called for 24 SVs, eight each in three circular orbital planes, but this was modified to six planes with four satellites each. The orbital

Figure 3(q): A GPS satellite

planes are centered on the Earth, not rotating with respect to the distant stars. The six planes have approximately 55° inclination (tilt relative to Earth's equator) and are separated by 60° right ascension of the ascending node (angle along the equator from a reference point to the orbit's intersection). The orbits are arranged so that at least six satellites are always within line of sight from almost everywhere on Earth's surface.

Orbiting at an altitude of approximately 20,200 kilometers (12,600 miles or 10,900 nautical miles; orbital radius of 26,600 km (16,500 mi or 14,400 NM)), each SV makes two complete orbits each sidereal day. The ground track of each satellite therefore repeats each (sidereal) day. This was very helpful during development, since even with just four satellites, correct alignment means all four are visible from one spot for a few hours each day. For military operations, the ground track repeat can be used to ensure good coverage in combat zones.

As of March 2008, there are 31 actively broadcasting satellites in the GPS constellation. The additional satellites improve the precision of GPS receiver calculations by providing redundant measurements. With the increased number of satellites, the constellation was changed to a nonuniform arrangement. Such an arrangement was shown to improve reliability and availability of the system, relative to a uniform system, when multiple satellites fail.

Some reports in 2008 indicated that the 32nd satellite was causing difficulties for some GPS receivers.

Figure 3(q): A GPS satellite

planes are centered on the Earth, not rotating with respect to the distant stars. The six planes have approximately 55° inclination (tilt relative to Earth's equator) and are separated by 60° right ascension of the ascending node (angle along the equator from a reference point to the orbit's intersection). The orbits are arranged so that at least six satellites are always within line of sight from almost everywhere on Earth's surface.

Orbiting at an altitude of approximately 20,200 kilometers (12,600 miles or 10,900 nautical miles; orbital radius of 26,600 km (16,500 mi or 14,400 NM)), each SV makes two complete orbits each sidereal day. The ground track of each satellite therefore repeats each (sidereal) day. This was very helpful during development, since even with just four satellites, correct alignment means all four are visible from one spot for a few hours each day. For military operations, the ground track repeat can be used to ensure good coverage in combat zones.

As of March 2008, there are 31 actively broadcasting satellites in the GPS constellation. The additional satellites improve the precision of GPS receiver calculations by providing redundant measurements. With the increased number of satellites, the constellation was changed to a nonuniform arrangement. Such an arrangement was shown to improve reliability and availability of the system, relative to a uniform system, when multiple satellites fail.

Some reports in 2008 indicated that the 32nd satellite was causing difficulties for some GPS receivers.

3.9.6Control segment

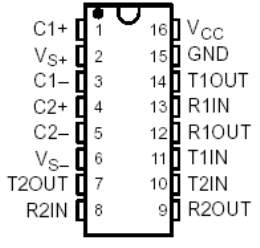

The flight paths of the satellites are tracked by US Air Force monitoring stations in Hawaii, Kwajalein, Ascension Island, Diego Garcia, and Colorado Springs, Colorado, along with monitor stations operated by the National Geospatial-Intelligence Agency (NGA). The tracking information is sent to the Air Force Space Command's master control station at Schriever Air Force Base in Colorado Springs, which is operated by the 2nd Space Operations Squadron (2 SOPS) of the United States Air Force (USAF). Then 2 SOPS contacts each GPS satellite regularly with a navigational update (using the ground antennas at Ascension Island, Diego Garcia, Kwajalein, and Colorado Springs). These updates synchronize the atomic clocks on board the satellites to within a few nanoseconds of each other, and adjust the ephemeris of each satellite's internal orbital model. The updates are created by a Kalman filter which uses inputs from the ground monitoring stations, space weather information, and various other inputs. Satellite maneuvers are not precise by GPS standards. So to change the orbit of a satellite, the satellite must be marked 'unhealthy', so receivers will not use it in their calculation. Then the maneuver can be carried out, and the resulting orbit tracked from the ground. Then the new ephemeris is uploaded and the satellite marked healthy again. User segment PS receivers come in a variety of formats, from devices integrated into cars, phones, and watches, to dedicated devices such as those shown here from manufacturers Trimble, Garmin and Leica (left to right). The user's GPS receiver is the user segment (US) of the GPS. In general, GPS receivers are composed of an antenna, tuned to the frequencies transmitted by the satellites, receiver-processors, and a highly-stable clock (often a crystal oscillator). They may also include a display for providing location and speed information to the user. A receiver is often described by its number of channels: this signifies how many satellites it can monitor simultaneously. Originally limited to four or five, this has progressively increased over the years so that, as of 2007, receivers typically have between 12 and 20 channels. A typical OEM GPS receiver module measuring 15×17 mm.

GPS receivers may include an input for differential corrections, using the RTCM SC-104 format. This is typically in the form of a RS-232 port at 4,800 bit/s speed. Data is actually sent at a much lower rate, which limits the accuracy of the signal sent using RTCM. Receivers with internal DGPS receivers can outperform those using external RTCM data. As of 2006, even low-cost units commonly include Wide Area Augmentation System (WAAS) receivers.

A typical OEM GPS receiver module measuring 15×17 mm.