Voter Circuit Improvement of Triple Modular Redundancy Technique

Info: 6379 words (26 pages) Dissertation

Published: 22nd Dec 2021

Tagged: Electronics

Abstract

Redundancy has been popular technique to design a fault tolerance system. As the hardware in a digital system are getting lower in price and software redundancy will consume more time and resources, hardware redundancy is useful mechanism to improve the reliability of the system. While an active hardware redundancy is used to detect the faults in the hardware component and recover the system from those faulty components, passive hardware redundancy is basically used to mask the faults in the hardware module. Triple Modular Redundancy is suitable example of hardware redundancy technique where three identical functional components are used and voting mechanism will take majority of inputs as the output of the system. However, a single point failure in the TMR will impede to improve the reliability of the system. This report will discuss on different mechanisms to improve the voter circuit of triple modular redundancy. A report presents a detail analysis on different techniques and comparison among these technique on basis cost and complexity to implement in triple modular redundancy to improve voter circuit.

Introduction

A failure of any components in a critical system could lead to catastrophic events like a human or economic loss. The divergent of a result of a non-critical system from its expected output will have little or no effect on the throughput of the system compared to that of a critical system [1]. So, it is imperative to ensure that every component is available at all the time and performing as it is expected and produce the desired output. With an implementation of fault tolerance mechanism in a critical system, there is an increase in the availability and reliability of a system’s components. A fault tolerant system is designed in such a way that it can detect the failures of components and isolate the defect components from the existing system and produce the desired output without interrupting the flow of the system. A fault tolerance system can be implemented through hardware redundancy and software redundancy. As the hardware redundancy is comparatively lower than software redundancy, it has become a popular technique to design a fault tolerance system [2].

A triple modular redundancy is one of the techniques to build fault tolerance system as it increases the reliability of the system through implementation of two out of three voting mechanism technique [3]. The voting mechanism has played a significant role in triple modular redundancy technique as it will decide an actual output out of three components. The majority outputs from the three components will be the actual output of the voting circuit. Despite its ability to generate consensual output from the three modules, the presence of single point failure i.e. the failure of the voting circuit itself could lead to inconsistency in the output the overall systems. This report includes a thorough description on fault tolerance, hardware redundancy, and triple modular redundancy technique. Furthermore, the report primarily focused on a mechanism to avoid the single point failure i.e. voting mechanism in the triple modular mechanism technique.

Background

The concept of fault, errors and failure plays crucial role while improving the dependability of the system. Most of the times, these three terms are used interchangeably in fault tolerance. However, each term has their own meaning and successful implementation of fault tolerance design must handle each of these terms.

Fault

It can be defined as the defect or flaws in the hardware or software component of the system. If it is hardware component, fault is considered as the defects whereas if it is software component, it is considered as the flaws in the software system. Faults are basically considered as the root of the failure of the systems, so, it is necessary to avoid any sort of the faults while integrating hardware or software of the system. On basis of the duration, fault can be permanent, transient or intermittent fault. While permanent fault occurs due to failure of components, physical damage of hardware or design and do not fix by themselves along with time, transient faults occur for short period of time and do not re-occur continuously. Meanwhile, intermittent fault moves in between fault and fault free operations in the system. Both transient and intermittent faults are occurred frequently compared to that of permanent faults in the system [4].

Error

Meanwhile, errors occur when output from the system is deviated from the expected output. So, when there is fault in the hardware components or software components, there will be inconsistency in the result from the components. Basically, error indicates the state that is invalid to the system specification and should not exist [5,6].

Failure

It can be defined as the incapacity of the system to produce desired results as specified in the system specification. When error occurs, a system will be in undesirable state and the result from the system will be different from the expected one. The system behavior will be changed which is considered as the failure of the system [5,6].

fault

Error

Failure

Figure 1 Flow of Fault, Error and Failure in the System

Redundancy

Redundancy is one of the efficient techniques to achieve fault tolerance mechanism in the digital system. As its name suggest, redundancy is basically an addition of hardware and software resources, information or time in a system more than it required to perform their normal operation. There are four redundancy techniques and they are:

- Software Redundancy

- Time Redundancy

- Information Redundancy

- Hardware Redundancy

Software Redundancy

While the physical defects in the hardware components can barely re-occurred once it is discovered and repair, fixing bugs in the software programs will create greater chance to create other errors in the coding. Despite the presence of different software development process, there are chances to develop error prone software due to novice developers, lack of testing or inadequate time and money for the full phase development of the software. N-version programming is one of the software fault-tolerance technique where a program writes for N times and execute in parallel to take majority output as a final output of the program. While this technique is an effective to mask the errors in the program, it will be costly and difficult to maintain all the version of the code. Likewise, a use of watchdog timers and timeouts, time redundancy for program or self-checking in the software allowed to detect the faults in the software. When a software runs for multiple times and compared the results, it is possible to identify the faults or bugs in the program.

Time Redundancy

The concept of time redundancy is to run the program multiples times in the presence of same hardware configuration and compare the produce results. It reduces the expense on expensive hardware addition and also avoid parallel execution of the programs. Since a program can be run multiple times in the same modules and compare the results to identify errors or faults, it will efficient compared hardware and software redundancy technique. Besides that, it is suitable for transient or intermittent faults as a frequent run of programs in same module will help to get majority output as the actual output of the system. However, one of the considerable disadvantages of time redundancy is the requirement of large amount of time to identify the faults and defects in the system compared to hardware and software system [8].

Information Redundancy

Here, there will be an addition of extra information along with data to ensure to integrity of the information changes during a storage or transmission. An error-detecting codes and correcting codes, and self-checking circuits are popular mechanism for information redundancy. Parity code is widely used for error-detection in the memory of the computer system. A parity bit is generated by a parity generator and data is encoding through computation of its parity. When there is changes in the computed parity bit with stored parity bit, there is an indication of data changes and error signal is sent to the processor of invalid memory data. On the other hand, data which are encoded with error-correcting codes contains both errors and adequate redundancy to recover the desired data. Meanwhile, self-checking circuit will produce valid output word when there is valid input and when there is existence of fault, it will produce invalid output code to detect the fault in the system [7].

Hardware Redundancy

Hardware redundancy can be achieved through the addition of extra hardware to the system. As the hardware components are getting cheaper with advancement of technology, it can be considered as suitable mechanism to achieve reliability in the system. Apart from that, it also does not require continue observation and will not take more time to identify and mask the error compared to other redundancy techniques. For example, an addition of processors, data or memory buses, power or even memories can easily achieve hardware redundancy. There are commonly three approaches to obtain hardware redundancy techniques and they are as follow

- Passive Redundancy

- Active Redundancy

- Hybrid Redundancy

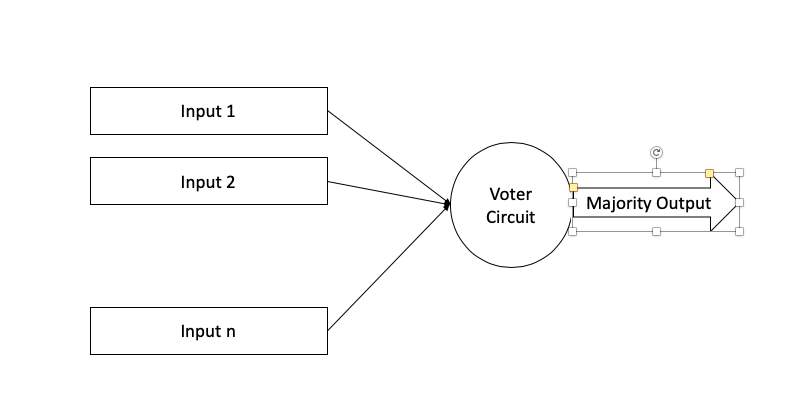

Passive redundancy is responsible for hiding and covering the faults in the hardware components rather than detecting those faults. It will produce the result based on polling mechanism and provide the correct output from the system despite the existing of faults in the components. When there are multiples faults than polling circuit can cover, then it cannot hide the faults and failure of the system is imminent. Triple modular redundancy and N modular redundancy are the suitable example of fault tasking technique through use of redundant hardware in the system [9].

Figure 2 N-modular hardware Redundancy

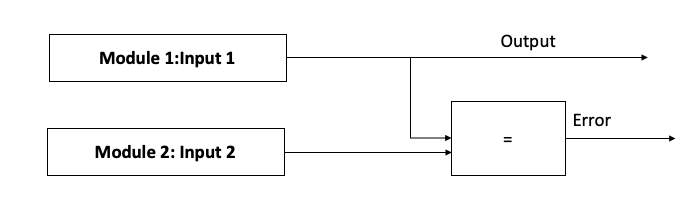

Similarly, active hardware redundancy is used to detect the faults in the components and recover from those faulty components. There are use of different techniques for fault detections and computation with duplication is one of the techniques where two duplicate modules execute identical computation in parallel and with use of comparator results are compared. If the results are not equal between two modules, an error signal will be produced.

After the detection of faults, no more activity is carried out until the system recover from the fault.

Figure 3 Comparison with Duplication

Meanwhile, in standby Sparing technique, a single module out of N modules will operate and responsible for the output of the system whereas remaining n-1 modules will remain as a spare. When there is failure of working module, spares will be switched and start to operate. Therefore, a standby sparing system having N modules will tolerate N-1 faults in the modules. Furthermore, Pair and spare technique combine both comparison technique and sparing technique to improve fault detects and recover. There is a use of two modules in parallel and when there is error after comparison, it will identify defected module and replaced it will spare modules. Apart from these techniques, timer mechanism can be used for error detection [10,11].

Besides active and passive redundancy techniques, hybrid redundancy technique, which includes features from both earlier techniques, is another hardware redundancy technique to identify faults in the components and recover from those faults. One of the approaches of hybrid redundancy technique is duplex-triplex architecture where two duplication with comparison technique along with TMR is used to mask the errors, detect the faults and remove those faults from the system to produce desirable output. One of the major disadvantages of hybrid redundancy is that the methods which are used to implement it are costly [12].

Triple Modular Redundancy

The concept of Triple Modular Redundancy is mainly based on redundancy of hardware components of the system. It is highly used to make system more reliable and continue to perform their operations against the soft errors. When an error occurs in sequential circuits, which indicates to the different storage in the system such as registers, memories, flip-flips and counters, there will be a change in the saved state in different storage and lead to the execution of the program different from the expected one. To minimize effects of soft errors, TMR is designed in microprocessors so that errors will not halt the flow of the program.

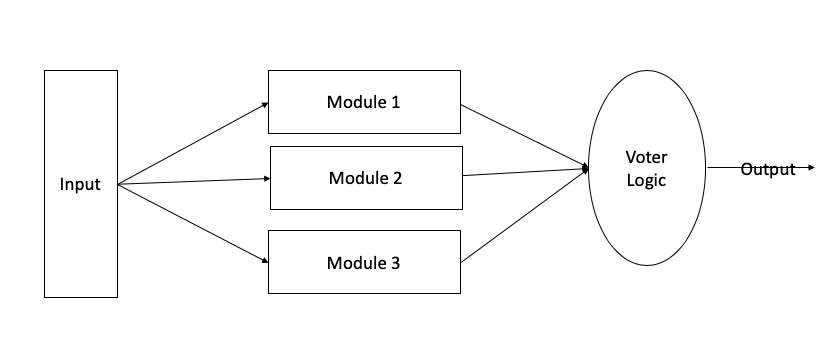

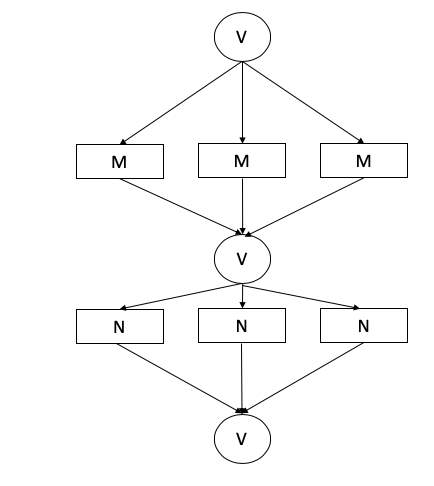

Figure 4 Triple Modular Redundancy Technique

The generalization of TMR technique in N modular redundancy technique. While there is presence of n modules in the N modular redundancy technique, TMR will have 3 identical functional hardware units to perform the operation. The concept of the TMR design is to use three duplicate modules which will take same input. All the operation within the module is same for all three of those modules, so, the use of input data is same of all three cases. On the top of the identical modules, there is apply of voting mechanism to get majority output as the actual output of the system. So, voter circuit will take all three outputs of the hardware unit as the input to the unit and majority of input will consider as the actual output of the system. For example, consider there are three hardware modules A, B and C in the system. All three modules are functionally identical, and all are supplied with 0 input. Among three modules, two produce output result as 1 whereas one module produces 0 as output. When all three outputs from module enter into voter Logic, E, it will perform some calculation to decide majority output from the modules, which in this case will be 1 and considered 1 as the output of the component. Since inputs in the voter logic are binary and number of inputs are in odd numbers, it will be easier to calculate majority inputs in the voter machine [13].

The basic purpose of Triple Modular Redundancy is to mask the errors exist in the functional unit of the system. So, it can be considered as the passive hardware redundancy technique to achieve the reliability of the system. The majority logic gate also known as voting logic is composed of simple AND-OR circuit. Consider a, b and c are three inputs from the modules to the logic gate, then it can be defined as ab V bc V ac. Furthermore, mathematically, the reliability of any system, R, can be calculated as the sum of the probabilities of success and fail events i.e.

R(system) = Rm3 + 3RM2(1- RM) = 3RM2 – 2 RM3

Here, the basic assumptions are made, and they are voting circuit does not fail, failures of three modules are independent from each other, system will not fail if none of three modules fails or exactly one module fails at a time. However, the major disadvantage of triple modular redundancy technique is its single point failure. While there can be made an assumption that voter circuit never fails but when it does, the reliability of whole system will be compromised. When all three modules are working perfectly, the failure of voter circuit can result different output from the system rather than actual correct output produce by the functional unit [15].

Literature Review

The purpose of fault tolerance system is to avoid a failure of the overall system in spite of existing faults in the different components. Redundancy has been a significant technique to assure fault tolerance design in the digital system. Among several redundancy techniques, hardware redundancy is constantly used to improve the reliability of the digital systems. While active hardware redundancy is useful to detect faults and recovery, passive hardware redundancy is useful to hide faults in hardware components. TMR is a passive hardware redundancy technique where faults are hidden, and only correct data are passed as output from the system [16].

V.M et al (2005) had discussed on the alternative technique to triple modular redundancy technique called Reduced Triple Modular Redundancy. It basically operates on lookup-table which is achieved after technology mapping stage. Rather than using three identical entire design, they preferred for the triplicating first and third category of the lookup table and there is a use of tri buffer-based majority voters to get the output from the system. The objective of their research is to handle single event failure, which mainly occurred to due excess charged induced from the radiation. As a result, it is highly influential to change the internal state of the data, mostly on memory elements like routing configuration bits and look up table entries. So, such errors could lead to change in bits in memory or table entries and completely produce unexpected output from the system. With the help of spare flip-flops of CLBs in combinational circuits, a number of insensitive LUTs are duplicated. They described a major disadvantage of using Triple Modular Redundancy technique is an excessive area overhead. Their proposed technique, RTMR, just required 99.61% of additional number of LUTs, which is almost 100% less that of LUTs required in normal TMR. Despite the use of a smaller number of additional LUTs in RTMR, it was able to provide high level of SEU immunity [17].

Another proposed approach to improve Triple modular redundancy is cascaded TMRs. They are mainly used in areas like pipeline process, Poly-Si TFT. Since there is use of multiple stages of TMR design to build the cascaded TMR, it is also known as Multi-stage TMR. The structure is designed in a such way that one output from the TMR will be the three inputs for the another TMR. It can be considered reliable if at least two inputs from each stage is provide correct value and end voter produce the accurate output. With use of multiple voters, it can impede the single point failure exist in the original Triple modular redundancy technique. While an original TMR has single voter, it cannot provide reliable result on the failure of voting system whereas cascaded triple modular redundancy technique can provide reliable result despite failure of voter.

Figure 1 Classical Cascaded Single Voter TMR Module

While original cascaded TMR consists of single point failure one voter, new proposed technique consists of multiple voter per stage. When there is use of single voter in the TMR, there are strict rule to achieve the reliability of the system. Meanwhile, when there is use of multiple voters in each stage of the TMR, it will increase the cost of designing and ultimately violate the cost-effective design. So, Yi, Chung and Kim (2015) proposed new cost-effective cascaded Triple modular redundancy which will improve the cost effectiveness of the design and also ensure there is loosen in the rules to bring the reliability to the system [18].

Meanwhile, the concept of TMR is to mask the faulty module in the system. When there is one faulty module in the system, it can continue to work and provide desired result. In order to execute the same task on the same hardware after the detection of TMR failure or replace the hardware, reload and restart, Shin and Kim (1994) proposed an adaptive recovery method by optimally choosing either RSHW or RHWR on basis of their cost effectiveness. They used Bayes theorem to update collect information of each state in the TMR system after each voting result. When there is TMR failure, the expected cost of RSHW will calculated on basis of all the likelihoods and those results are compared with RHWR.

After continuing increase in the number of unsuccessful RSHWs, permanent TMR failure will be increased and eventually there is increase in the cost of RSHW. As more than 90% faults in the system are known as transient faults or non-permanent faults and around 2% faults are permanent faults, a simple re-execution of the task will be an effective process to recover from most of the TMR failures. Such re-execution of task will help to eliminate hardware cost arise due to replacement of large chunk of hardware failures, reduce recovery time arise through the replacement of hardware, system configuration and system restart. The adaptive method of RSHW calculate the state with all possible likelihoods state in the system and later gauge the RSHW or RHWR based on their expected cost when the system reaches in one of the estimated states. When the number of unsuccessful RSHWs exceeds the maximum number of RSHWs allowable or estimated cost of RSHW exceed that of RSHW, then RHWR will be invoked [19].

Furthermore, Patooghy et.al (2006) discussed on distributed voting mechanism to overcome the existing problem of the single point failure in the Triple Modular Redundancy. Their ideas utilized the use of time redundancy and disagreement detector features to overcome the issue. A method is experimented with vertex2Pro and Vertex4 Xilinx FPGA to demonstrate the reliability and improve mean time failure of a TM system. They highlighted despite the continue research to improve the voting circuit in the TMR system, many of those works are based on certain level of assumptions which makes existing problem simple but unrealistic. One common example of such assumption is many of researches are based on neglecting the single point failure to improve the reliability of the system. Their proposed method would mask the permanent and transient faults which occurred in the voter of a TMR system with help of time redundancy, Triple modular redundancy with disagreement detector and use of n spares voter in the system. The number of spare voters used in the system will help to decide how many faults it can cover in the system. One of the benefits of their proposed method is that distribution of decision between voter and disagreement detector. However, one of the disadvantages of their proposed method is certain level of delay to produce the output due to comparison between distributed decision maker [20].

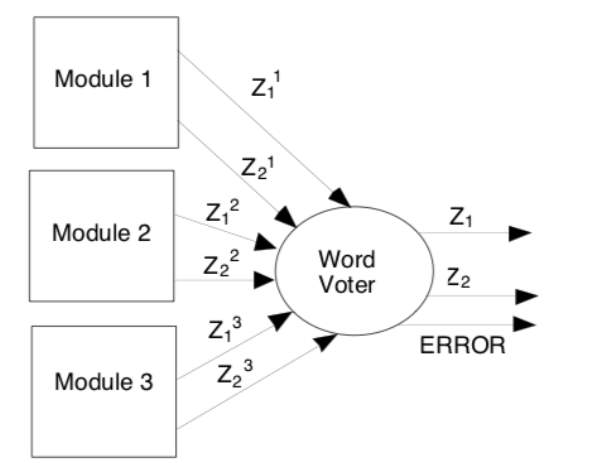

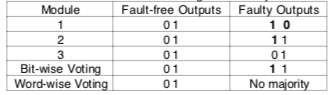

The use of word voter over conventional voter has their own advantage to ensure the data integrity. Mitra and McCluskey (2000) has discussed on word voter and presented their implementation with compare to bit by bit voting design in conventional voter system. They had compared area and delay overhead of word-voter design with bit by bit voter. The use of word-voter will have to improve the capabilities of Triple modular system to protect against common-mode and multiple module failures. There is necessary of extra hardware to build the word voter which is an order of one 2-input logic gate and three XNOR gates for each output of the system. Meanwhile, the word voter design can be modified to guarantee that data outputs without the error signal in absence of extra gate.

Figure 2 TMR system with Word Voter

Figure 3 voting mechanism in TMR

Here, the above to figure explaining the voting mechanism for both bit by bit voting mechanism and word voting mechanism. While bit by bit voting mechanism will considered each bit of the input to find the errors in the faulty module, word-wise voting mechanism will take both of the inputs and compared to find the errors in the module [21] .

While TMR supports to improve the reliability of systems, it’s single point failure i.e. voting logic failure could cause the failure of an overall system. Sadeghi, Soltan, and Khayyambashi [22] has argued that despite a simple structure of TMR model, an existence of voter logic as a weaker point will lead to a failure of the overall system. When there is a fault in a single hardware component, a voter can mask those faults by generating correct output from the system. However, if there are any faults on a voter, it will produce an inconsistent and incorrect output which can lead to the failure of a system. Therefore, they have proposed to use three voters instead of one voter so that the probability of voter logic failure will be reduced and a failure of one voter can be covered by other two voters in the system.

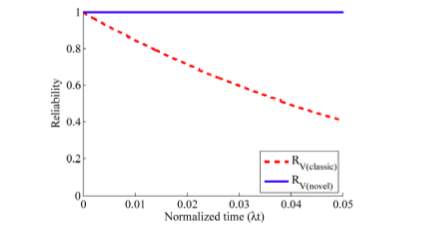

As the reliability of a voter must be high to improve the overall reliability of the system, an assumption of voter always produces a correct result or remain fault free weaken to produce fault tolerance design. Moslem and Václav [23] have proposed novel fault tolerant voter circuit design using wired-logic to make voter itself to tolerant faults and support the reliability of a system. An open drain CMOS NAND gate, which comprises only 2 series-connected n-channels are used to make fault-tolerant voter. Furthermore, novel voter circuit design can be expanded for N- modular redundancy system where N is odd integer and greater than or equal to five.

While there are different methods which are proposed to improve the reliability of systems and make fault tolerant voter circuit, some proposed methods increased the complexity with use of multiple multiplexer and priority encoders. Meanwhile, other proposed methods are lack of inextensibility due to which such module will only support on particular models rather than generalized model. A novel fault tolerant voter circuit has reduced the complexity in its design and further support for generalized hardware redundancy methods.

Research Methodology

Triple modular redundancy method has been useful technique to improve the reliability of the system. While TMR has ability to mask the fault exist in of the module, it will not able to minimize the fault exist in the voter circuit. It is also called single point failure in the TMR system and failure of voter circuit can compromise the reliability of the system. This report has performed primary research on improving the voter circuit of the Triple modular redundancy system. Meanwhile, the report also performs the secondary research on improving the reliability of triple modular redundancy system with consideration of TMR failure, and so on.

The problem statement of the report clearly states that voter circuit in the triple modular system fails can lead to the failure of the system. Voter circuit is used to produce an output from the majority of the input to the voter. Since there is use of three identical modules in the TMR with providing same input on each of those modules, voter circuit can receive either same input from all the modules or can receive at least two different input from three modules. The report has identified different assumptions that are made while designing the triple modular redundancy and elaborate and eliminated those assumption to identify actual technique that would help to improve the voter circuit of the system. Mainly, research finds some of the assumptions common on different implementation technique and they are as follow

- Voter circuit never fails

- There will be no faults on two modules at once, which means only one module can have fault to implement TMR design

Both of these assumptions have made significant role in designing simple Triple Modular Redundancy system.

Since a research is a qualitative research, it has described different terminology associated with TMR technique. The distinguish between fault, error and failures in digital system followed by different redundancy techniques such as hardware, software, time and information redundancy technique helps to enlist the advantage and disadvantage of each redundancy technique. The research illustrated that hardware redundancy is more common practice to build reliability in digital system compared to that on software redundancy. As hardware devices are cheaper along with advancement in technology, it can be useful to design fault tolerance system. On the other hand, software redundancy required multiple times run of same program in parallel, which will consume both resources and time to find the faults in the program and fix those bugs. Furthermore, research also identifies time redundancy can be useful to avoid the use of additional hardware and need of parallel run of the program. However, since it executes multiple times of the program to identify the bugs in the program, it will delay overall execution of the program.

Meanwhile, to improve the voter circuit, this report has measured the cost effectiveness and complexity of proposed design to improve reliability of the voter circuit. A literature review from different papers were observed as a part of the survey to identify the potential design to improve the voter circuit of Triple modular redundancy system. In addition, research report has compared the theoretical knowledge of different papers rather than collecting sample data and applying numerical formula to compare the result. Based on results from different papers, benefits and drawbacks of each design is identified and classified to choose appropriate design method to resolve an issue associated with the single point failure. While the paper has tried to minimize unnecessary assumptions but has not completely avoid all the assumptions exist while designing the system.

Result

The report has reviewed several research papers related to reliability of triple modular redundancy. It is observed that triple modular redundancy has simpler structure to design and effectively handle the fault masking of hardware components. The observation of results from different papers derived that the assumptions such as no failure of two hardware components at once and simply voting logic will never fail has weaken the reliability of triple modular redundancy technique. Meanwhile, a research also finds despite many of these proposed techniques are viable to improve voter, a complexity, inextensibility, and dependency on the other components make difficult to implement. By comparing above factors, a novel fault-tolerant voter circuit design is suitable to improve voter logic as it overcomes the complexity, inextensibility, and dependency and able to provide reliability to the TMR system. It has reduced the complexity required to increase the reliability of the voter circuit as there is only use of twelve transistors and one pull-up resistor for a voter. Furthermore, the dependency due to the network on one gate in the voter to produce the final output is also reduced.

Figure 1 Reliability Comparison between classic voter and novel voter

With use of open-drain NAND gates, which consists of only 2 series-connected n-channels, a simple and reliable voter circuit can be generated.

Conclusion and Future Work

Conclusion

Hardware redundancy is useful to improve the reliability of the system. Although the structure of triple modular redundancy is simple and cost effective, a single point failure i.e. voter circuit could cause the failure of the overall system. Meanwhile, different techniques were proposed to improve the reliability of the triple modular redundancy, however, many of these techniques were based on assumptions that no two modules will fail at the same time and voter circuit will never fails. The report has performed detail analysis on some techniques which will be useful to improve the voter circuit in the system.

Future Work

This research remains focused on improving voter circuit of the triple modular redundancy. The report studies several literature review papers to analysis the technique to improve the voter mechanism so that the reliability of the triple modular redundancy will not compromise due to the single point failure in the TMR. A further detailed research and perform the analysis through collection of data will provide sheer information regarding suitable technique to improve reliability of the system. Although the report has performed cost and complexity analysis to select appropriate technique for voter, use of numerical data will further evidence to select appropriate mechanism.

References

[1] Kim, M. H., Lee, S., & Lee, K. C. (2010). Kalman predictive redundancy system for fault tolerance of safety-critical systems. IEEE Transactions on Industrial Informatics, 6(1), 46-53.

[2] Shooman, M. L. (2003). Reliability of computer systems and networks: fault tolerance, analysis, and design. John Wiley & Sons.

[3] Lyons, R. E., & Vanderkulk, W. (1962). The use of triple-modular redundancy to improve computer reliability. IBM Journal of Research and Development, 6(2), 200-209.

[4] Nelson, V. P. (1990). Fault-tolerant computing: Fundamental concepts. Computer, 23(7), 19-25.

[5] Dal Cin, M., & Hohl, W. (Eds.). (2012). Fault-Tolerant Computing Systems: Tests, Diagnosis, Fault Treatment 5th International GI/ITG/GMA Conference Nürnberg, September 25–27, 1991 Proceedings (Vol. 283). Springer Science & Business Media.

[6] Kaur, J., & Kinger, S. (2014). Analysis of different techniques used for fault tolerance. IJCSIT) International Journal of Computer Science and Information Technologies, 5(3), 4086-4090.

[7] Dubrova, E. (2013). Fault-tolerant design (pp. 55-65). New York: Springer.

[8] Nicolaidis, M. (1999, April). Time redundancy based soft-error tolerance to rescue nanometer technologies. In vts (p. 86). IEEE.

[9] SADEGHI, M., SOLTAN, H., & KHAYYAMBASHI, M. (2015). The study of hardware redundancy techniques to provide a fault tolerant system. Cumhuriyet Science Journal, 36(4), 236-245.

[10] Oliveira, D. A., Rech, P., Quinn, H. M., Fairbanks, T. D., Monroe, L., Michalak, S. E., … & Carro, L. (2014). Modern GPUs radiation sensitivity evaluation and mitigation through duplication with comparison. IEEE Transactions on Nuclear Science, 61(6), 3115-3122.

[11] Dumbri, A. C., & Procyk, F. J. (1985). U.S. Patent No. 4,494,220. Washington, DC: U.S. Patent and Trademark Office.

[12] Lee, S., Lee, S., Lee, K.-C., & Kim, M.-H. (2017). Analytical hybrid redundancy system for the fault tolerance of advanced driver assistance systems. Proceedings of the Institution of Mechanical Engineers, Part D: Journal of Automobile Engineering, 231(12), 1660–1665. https://doi.org/10.1177/0954407016684265

[13] Anjankar, S. C., & Kolte, M. T. (2014). Fault Tolerant and Correction System Using Triple Modular Redundancy. International Journal of Emerging Engineering Research and Technology, 2(2), 187-191.

[14] Avizienis, A. (1985). The N-version approach to fault-tolerant software. IEEE Transactions on software engineering, (12), 1491-1501.

[15] Rahman, M., Rafique, S., & Alam, M. (2017). A Fault Tolerant Voter Circuit for Triple Modular Redundant System. Journal of Electrical and Electronic Engineering, Vol5, (5), 149-159.

[16] V. M. Noor Mohammad, Vikram Chandrasekhar, V. Kamakoti, “Reduced triple modular redundancy for tolerating seus in sram-based fpgas”, Proceedings of NASA International Conference on Military Applications in Programmable Logic Devices (MAPLD) September 2005, september 2005.

[17] Yi, H. J., Chung, T. S., & Kim, S. (2015). A Reliability Analysis of Cascaded TMR Systems. In Information Science and Applications (pp. 369-376). Springer, Berlin, Heidelberg.

[18] Shin, K. G., & Kim, H. (1994). A time redundancy approach to TMR failures using fault-state likelihoods. IEEE Transactions on Computers, 43(10), 1151-1162.

[19] Patooghy, A., Miremadi, S. G., Javadtalab, A., Fazeli, M., & Farazmand, N. (2006, September). A solution to single point of failure using voter replication and disagreement detection. In Dependable, Autonomic and Secure Computing, 2nd IEEE International Symposium on (pp. 171-176). IEEE.

[20] Mitra, S., & McCluskey, E. J. (2000). Word-voter: a new voter design for triple modular redundant systems. In VLSI Test Symposium, 2000. Proceedings. 18th IEEE (pp. 465-470). IEEE.

[21] SADEGHI, M., SOLTAN, H., & KHAYYAMBASHI, M. (2015). The study of hardware redundancy techniques to provide a fault tolerant system. Cumhuriyet Science Journal, 36(4), 236-245.

[22] Sheble, N. (2003). More is always better when it’s critical. INTECH-RESEARCH TRIANGLE PARK NC-, 50(10), 66-70.

[23] Amiri, M., & Přenosil, V. (2013). Design of a simple reliable voter for modular redundancy implementations. DISTANCE LEARNING, SIMULATION AND COMMUNICATION 2013, 8.

Cite This Work

To export a reference to this article please select a referencing stye below:

Related Services

View allRelated Content

All TagsContent relating to: "Electronics"

Electronics regards the science and technology involved in the development of electrical circuits and electronic devices and equipment that use them.

Related Articles

DMCA / Removal Request

If you are the original writer of this dissertation and no longer wish to have your work published on the UKDiss.com website then please: